【FPGA】基本实验步骤演示 | Verilog编码 | 运行合成 | 设备/引脚分配 | 综合/实施 | 设备配置 | 以最简单的逻辑非为例

| 阿里云国内75折 回扣 微信号:monov8 |

| 阿里云国际,腾讯云国际,低至75折。AWS 93折 免费开户实名账号 代冲值 优惠多多 微信号:monov8 飞机:@monov6 |

写在前面本章的目的是让你理解与门、或门和非门的行为并使用 Verilog 语言实现多输入与门、或门和非门。在生成输入信号之后你需要通过模拟来验证这些门的操作并使用 FPGA 来验证 Verilog 实现的电路的行为。

0x00 引入与门、或门与非门

构成数字系统电路的最基本元素以集成电路的形式实现逻辑代数中0和1的运算作为这些逻辑代数基础的门有与门、或门、非门等它们的组合可以生成多种形式的门。

0x01 与门AND

接收两个或多个输入信号的门所有信号都必须是高信号才能输出高信号除此之外还必须输出低信号。布尔表达式中的乘法表示如下

0x02 或门OR

接收两个或多个信号其中一个信号在高信号时输出高值在没有高信号时输出低值。布尔表达式中的乘法表示如下

0x03 非门NOT

NOT 门Inverter通过反转输入值输出。BUFFER 门由两个 NOT gate 组成信号不变但增强了信号强度。

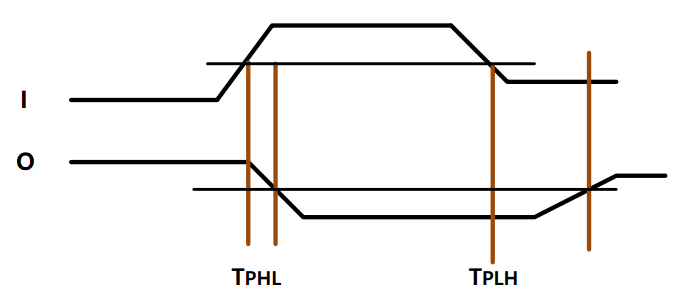

0x04 传播延迟Propagation Delay Time

从输入到输出的信号值变化所需的平均时间影响逻辑门的延迟和数量。

0x05 验证 FPGA 行为

动作验证阶段

- Verilog coding

- Run synthesis

- Device/Pin assignment

- Synthesis / Implement

- Device configuration

例子非门 Verilog coding

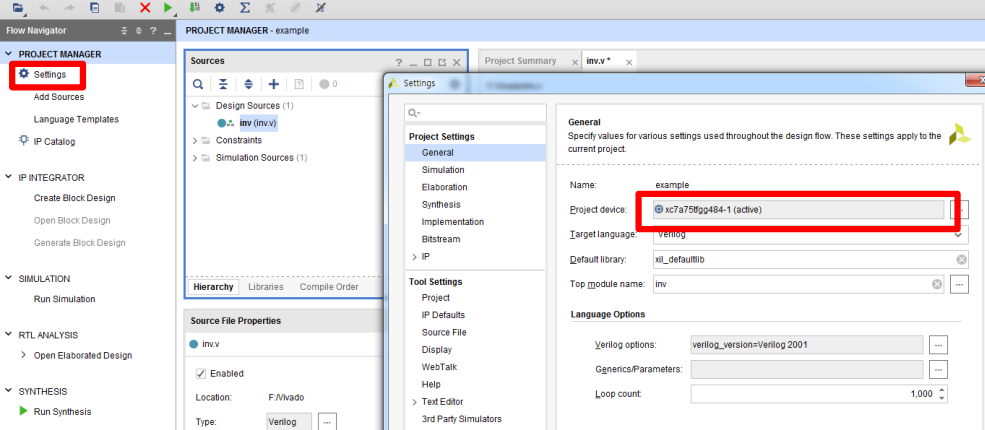

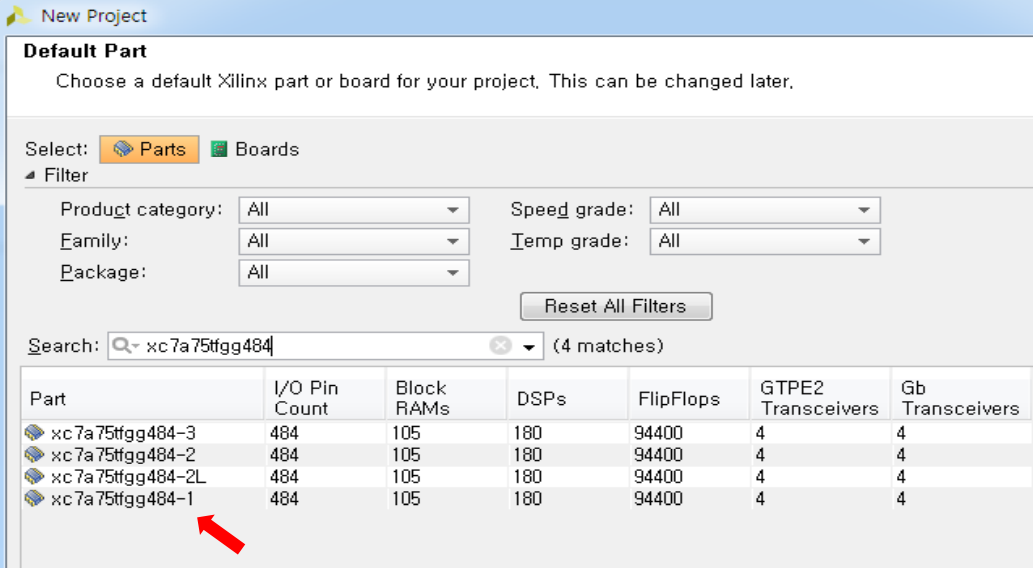

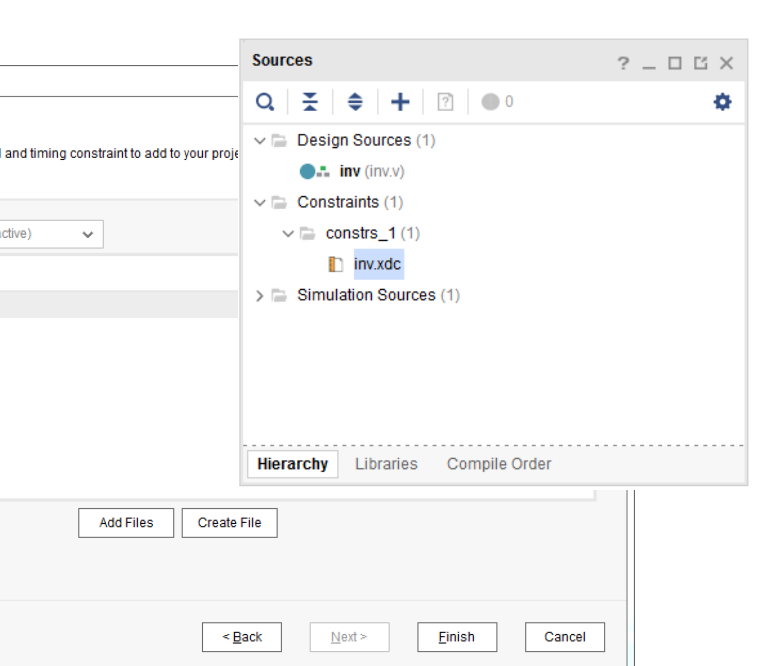

Device assignment

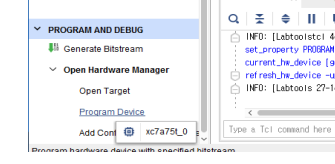

Device assignment → Device : xc7a75tfgg484(Artix7)

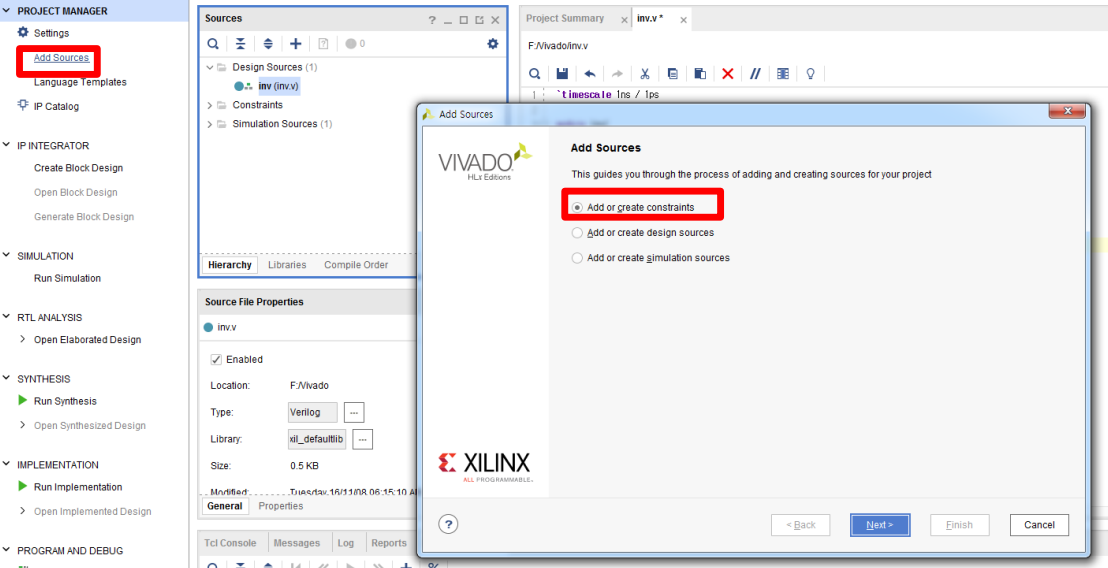

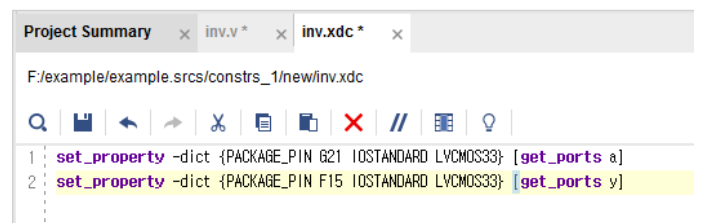

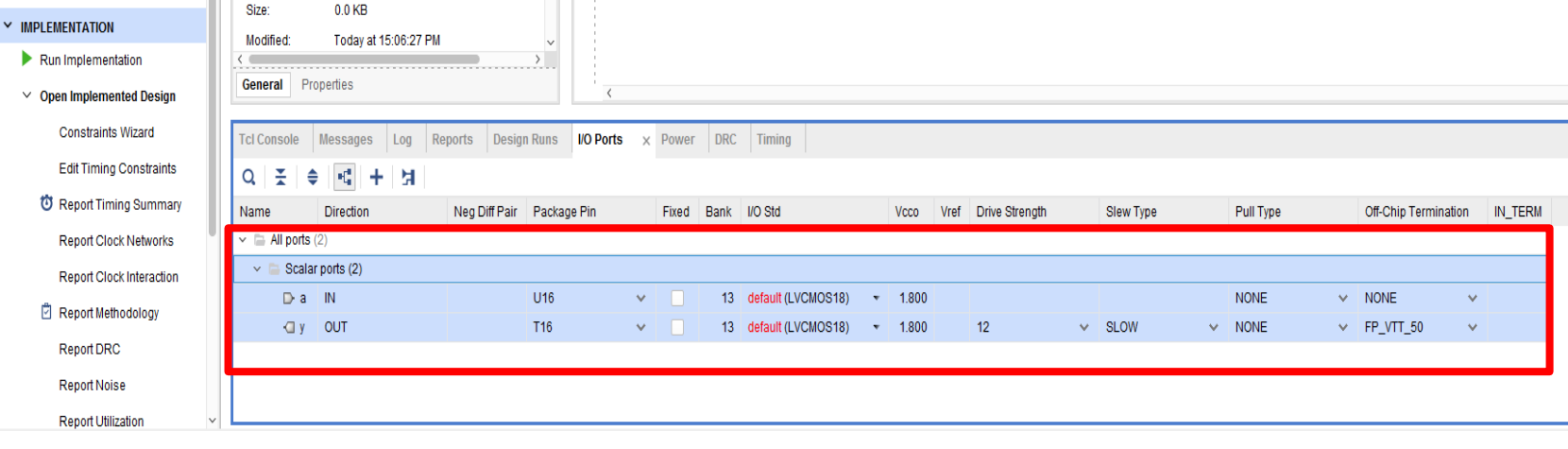

Pin assignment

链接你希望在 FPGA pin list 中分配的 Pin 和 Verilog 源端口

set_property -dict {PACKAGE_PIN G21 IOSTANDARD LVCMOS33} [get_ports a]

set_property -dict {PACKAGE_PIN F15 IOSTANDARD LVCMOS33} [get_ports y]

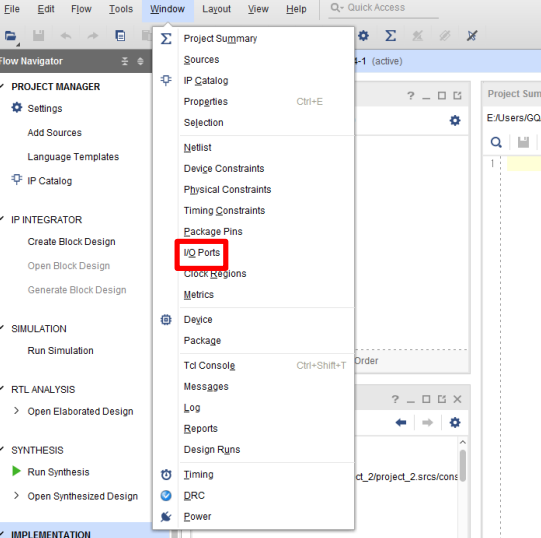

Synthesis / Implementation

Device configuration

我的板子是 FPGA Starter Kit Ⅲ

板子的初始化状态如下所示

Open Target → 点击 auto connect自动连接

选择 Program Device

🚩 输出结果演示

0x06 练习4-input 或门

比较A和B的布尔表达式

完成A和B的 Verilog 编码

通过A和B模拟比较输出结果

比较A和B的动作与 FPGA 的动作

完成 4-input OR gate 的真值表

💬 or.v

`timescale 1ns / 1ps

module input_4_OR(

input A,

input B,

input C,

input D,

output E,

output F,

output G

);

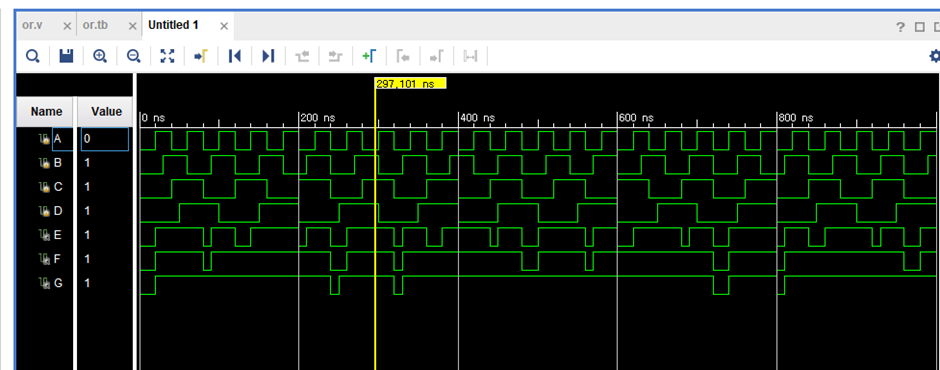

assign E = A | B;

assign F = C | E;

assign G = D | F;

endmodule💬 or.tb

`timescale 1ns / 1ps

module input_4_OR_tb;

reg A;

reg B;

reg C;

reg D;

wire E;

wire F;

wire G;

input_4_OR u_input_4_OR(

.A(A ),

.B(B ),

.C(C ),

.D(D ),

.E(E ),

.F(F ),

.G(G )

);

initial begin

A = 1'b0;

B = 1'b0;

C = 1'b0;

D = 1'b0;

end

always@(A or B or C or D) begin

A <= #20 ~A;

B <= #30 ~B;

C <= #40 ~C;

D <= #50 ~D;

end

initial begin

#1000

$finish;

end

endmodule🚩 Simulation 结果如下

Verilog编码 | 运行合成 | 设备/引脚分配 | 综合/实施 | 设备配置

📌 [ 笔者 ] 王亦优

📃 [ 更新 ] 2023.1.3

❌ [ 勘误 ] /* 暂无 */

📜 [ 声明 ] 由于作者水平有限本文有错误和不准确之处在所难免

本人也很想知道这些错误恳望读者批评指正| 📜 参考资料 Introduction to Logic and Computer Design, Alan Marcovitz, McGrawHill, 2008 Microsoft. MSDN(Microsoft Developer Network)[EB/OL]. []. . 百度百科[EB/OL]. []. https://baike.baidu.com/. |