基于FPGA的时间数字转换(TDC)设计(三)

| 阿里云国内75折 回扣 微信号:monov8 |

| 阿里云国际,腾讯云国际,低至75折。AWS 93折 免费开户实名账号 代冲值 优惠多多 微信号:monov8 飞机:@monov6 |

1.多相位TDC计时测试

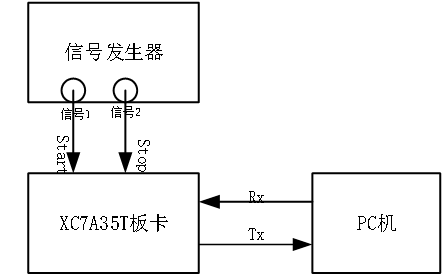

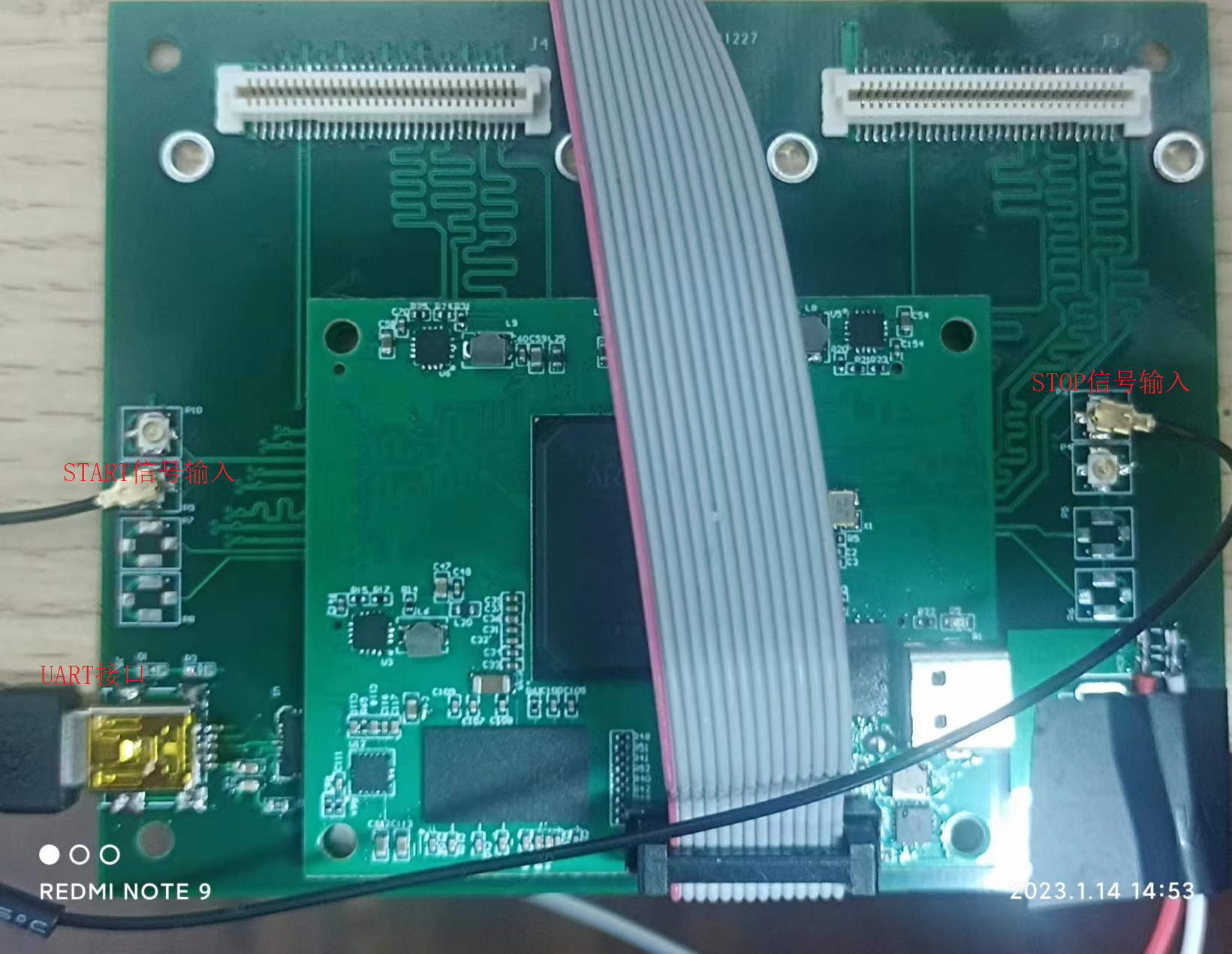

以下为多相位TDC计时的测试。图1为多相位TDC计时的测试框图,利用信号发生器,产生两路同相位、具有固定延时的脉冲信号,一路作为Start信号,另外一路作为Stop信号。由于分辨率为312.5ps,因此以312.5ps为步进,对Stop信号进行延时,扫描一个周期,通过UART接口传输给上位机软件,通过Matlab进行分析。图2为整个硬件实物图,由XC7A35T核心板和底板组成,输入的两路信号Start、Stop通过IPEX接口,连接至FPGA IO口。FPGA板卡采用上海卫红实业公司生产的XC7A35T核心板,表1为板卡详细参数。

图1 多相位TDC计时测试框图

图2 XC7A35T核心板+底板实物图

表1:XC7A35T核心板详细参数