DDR3 SDRAM分析-CSDN博客

| 阿里云国内75折 回扣 微信号:monov8 |

| 阿里云国际,腾讯云国际,低至75折。AWS 93折 免费开户实名账号 代冲值 优惠多多 微信号:monov8 飞机:@monov6 |

以镁光的MT41K2G4、MT41K1G8、MT41K512M16为例说明

一、地址构成

地址构成如表1所示主要包括Row address、Bank address、Column address三组地址表中2 Gig x 4、1 Gig x 8、512 Meg x 16分别对应于MT41K2G4、MT41K1G8、MT41K512M16三款DDR3 SDRAM这三款芯片容量大小均为8Gbit。

| Parameter | 2 Gig x 4 | 1 Gig x 8 | 512 Meg x 16 |

|---|---|---|---|

| Configuration | 256 Meg x 4 x 8 banks | 128 Meg x 8 x 8 banks | 64 Meg x 16 x 8 banks |

| Refresh count | 8K | 8K | 8K |

| Row address | 64K (A[15:0]) | 64K (A[15:0]) | 64K (A[15:0]) |

| Bank address | 8 (BA[2:0]) | 8 (BA[2:0]) | 8 (BA[2:0]) |

| Column address | 4K (A[13,11, 9:0]) | 2K (A[11,9:0]) | 1K (A[9:0]) |

| Page size | 2KB | 2KB | 2KB |

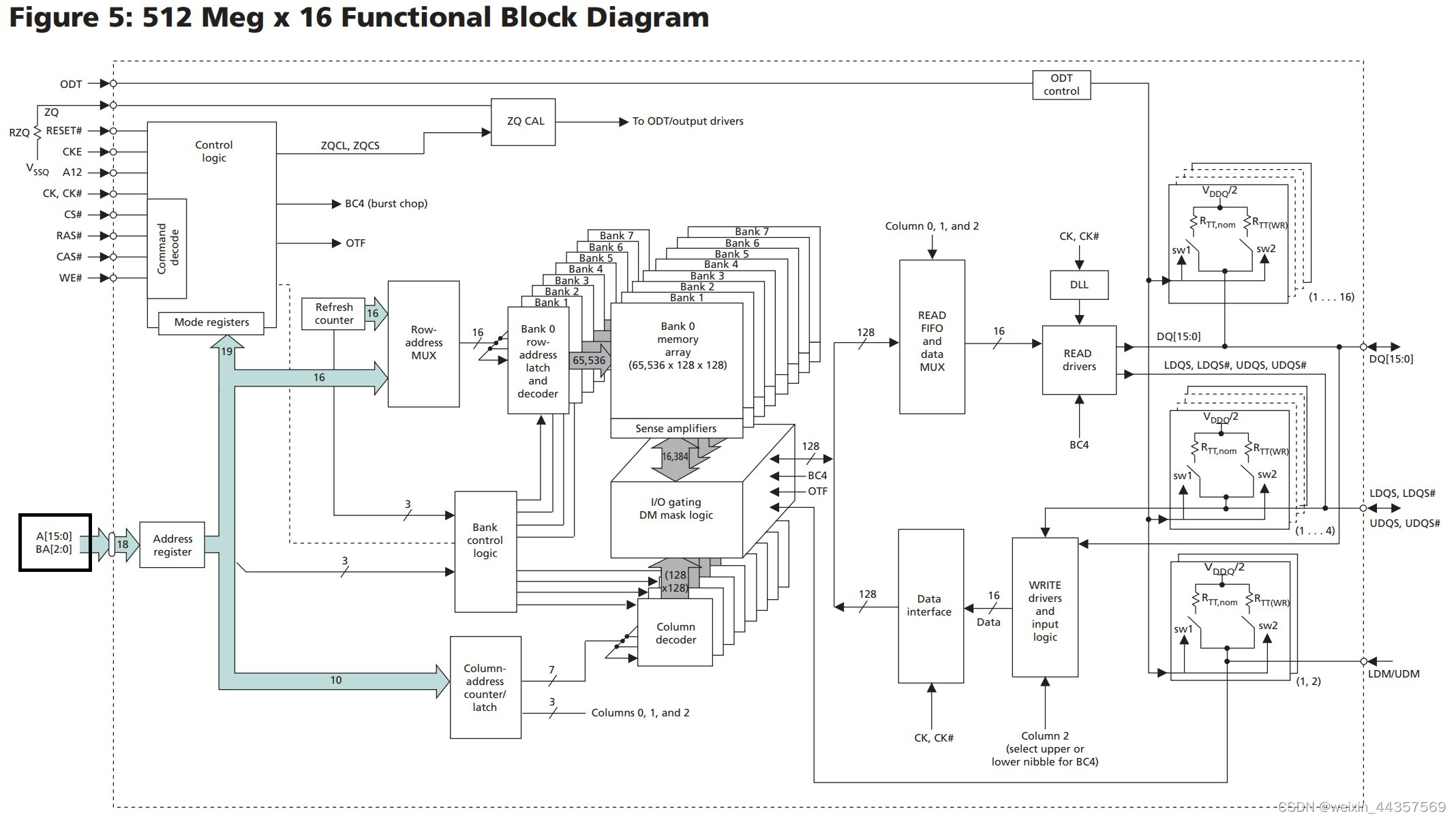

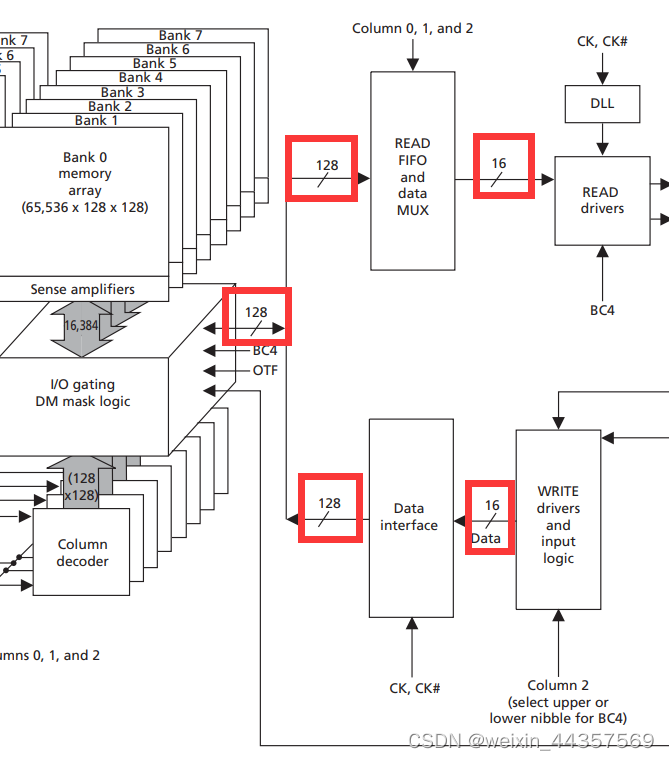

下面以MT41K512M16为例进行分析。在手册中可以看到该芯片的结构示意图如图1所示在图中左侧可以看到有A[15:0]和BA[2:0]两组地址线地址线的对应关系在表1中有说明Row address与Column address共用A[15:0]地址线在不同的时间分别输入这两组地址。

二、寻址方式 存储结构

寻址方式通过输入的地址信号定位到SDRAM中的某一个存储单元从而可以进行读写操作因此分析寻址方式同时也就是分析其存储结构。

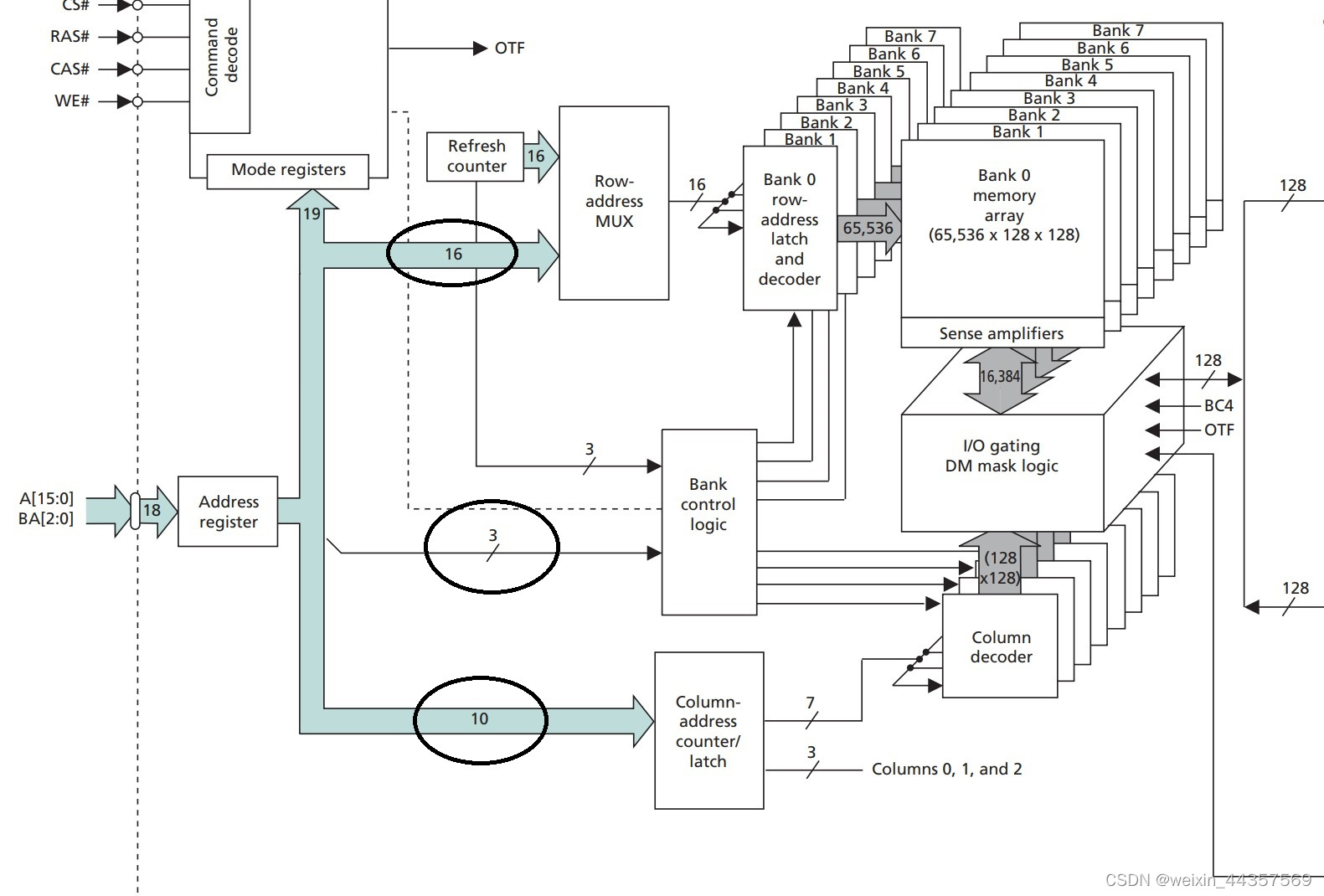

放大分析图1左下角有关寻址的部分如图2所示可以看到输入的地址信号有三条走向分别对应Row、Bank、Column三组地址位宽也与三组地址相一致。

Bank address

首先是Bank地址每个SDRAM具有8个Bank由3位Bank地址可以寻址。由图中可以看到每个Bank容量大小为65536128

128=1Gbit。Bank内的寻址由Row、Column寻址因此每个Bank可以理解为由许多最小存储单元组成的二维平面。

Row address行地址

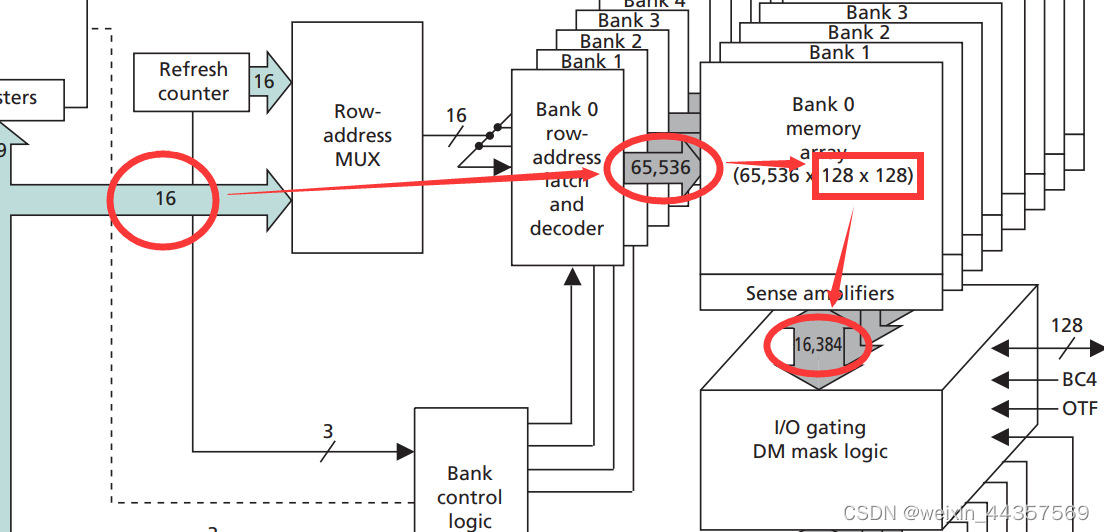

Bank内寻址先是行地址16位宽具有2^16=65536个单元的寻址能力对应于bank内部的65536个行每个行内有128128=16384=16Kbit的容量。

Column address列地址

Bank内列地址与行地址寻址方式有所不同。

按常理分析10位宽的地址本应有2^10=1024个单元的寻址能力然后每个最小单元存储位宽16bit总共102416=16384=16Kbit正好与行地址中的分析结论一致许多地方在分析SDRAM存储容量时也是这样分析的但是实际上这样是有问题的。

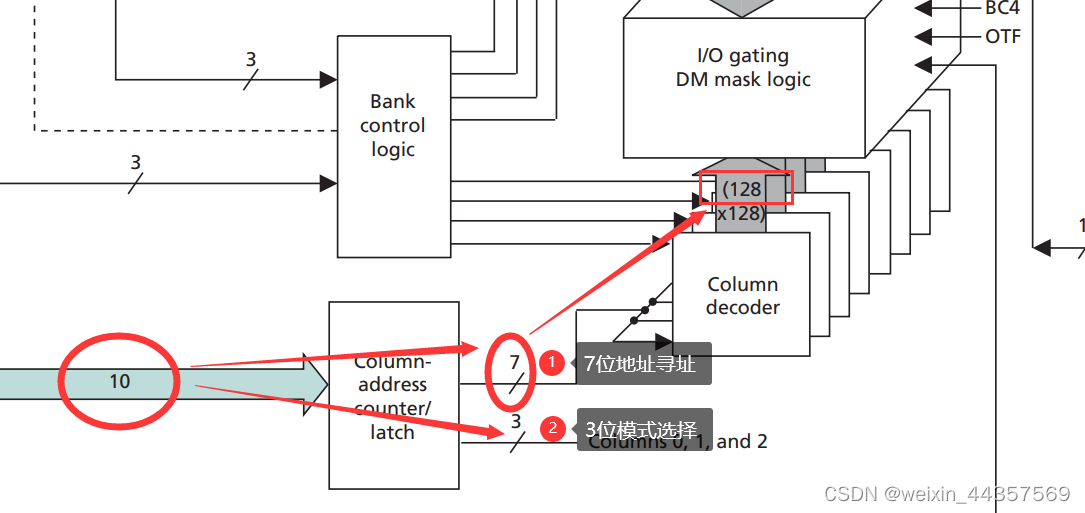

如下图所示我们可以看到实际上10位的地址只有高7位用于寻址低3位另有他用。高7位实际的列寻址能力为2^7=128对应每个最小存储单元Cell具有128bit的存储容量低3位则用于突发模式的选择设置。

三、预加载Prefetch与突发Burst

预加载Prefetch

预加载是DDR提出的技术DDR在外部时钟芯片IO的上下沿同时进行数据存取而内部时钟芯片存储单元仅在上升沿进行数据存取因此提出了2n-bit预加载n为芯片IO宽度最小存储单元Cell位宽为芯片IO位宽的两倍解决时钟带来的数据量不平衡问题而SDR中没有双沿传输也就没有预加载的技术Cell的位宽就是芯片IO的位宽。Cell的位宽也是每个Cell的存储容量

DDR2时代外部时钟是内部时钟的两倍并且仍然采用上下沿传输数据因此采用了4n-bit预加载Cell位宽为芯片IO宽度的4倍而DDR3和DDR4外部时钟为内部时钟四倍采用8n-bit预加载Cell位宽为芯片IO宽度的8倍。通过预加载的技术可以使Cell的频率较低的情况下获得较高的数据带宽。

突发Burst

突发是指连续进行数据传输突发长度Burst LengthBL是指连续数据传输的长度。

上面预加载中我们提到DDR3采用8n-bit预加载内部Cell每次传输的数据为IO宽度的8倍因此DDR3的BL常常为8也有长度为4的BC 4此时通常是另外4次传输不发生或认为无效。

DDR2采用4n-bit预加载BL有4或8两种为8的时候相当于每次发生两个4n-bit预加载。

四、Column address列地址剩余问题

再说上面列地址中残余的两个问题

- 低3位列地址的作用

- 为什么每个Cell具有128位

上述中以MT41K512M16为例说明芯片IO位宽为16DDR3具有8n-bit的预加载所以内部Cell的宽度就是168=128bit。

如下图所示芯片内部左侧区域时钟为内部时钟数据宽度为128位右侧时钟为外部时钟数据宽度为16位。左侧1次时钟上升沿传输128位的数据提供右侧4次时钟上下沿共8次16位数据的传输。

当给出一个地址时可以传输这个地址对应Cell的128位数据到FIFO再通过4次时钟上下沿的8次数据传输到外部也就完成了BL=8的一次突发传输。而芯片IO的8次传输从128位到16位需要一个8路选择器来决定这128bit的输出顺序列地址的低3位参与了这个选择顺序的过程。

突发传输的顺序由Burst Order与Burst Type来决定如下图所示

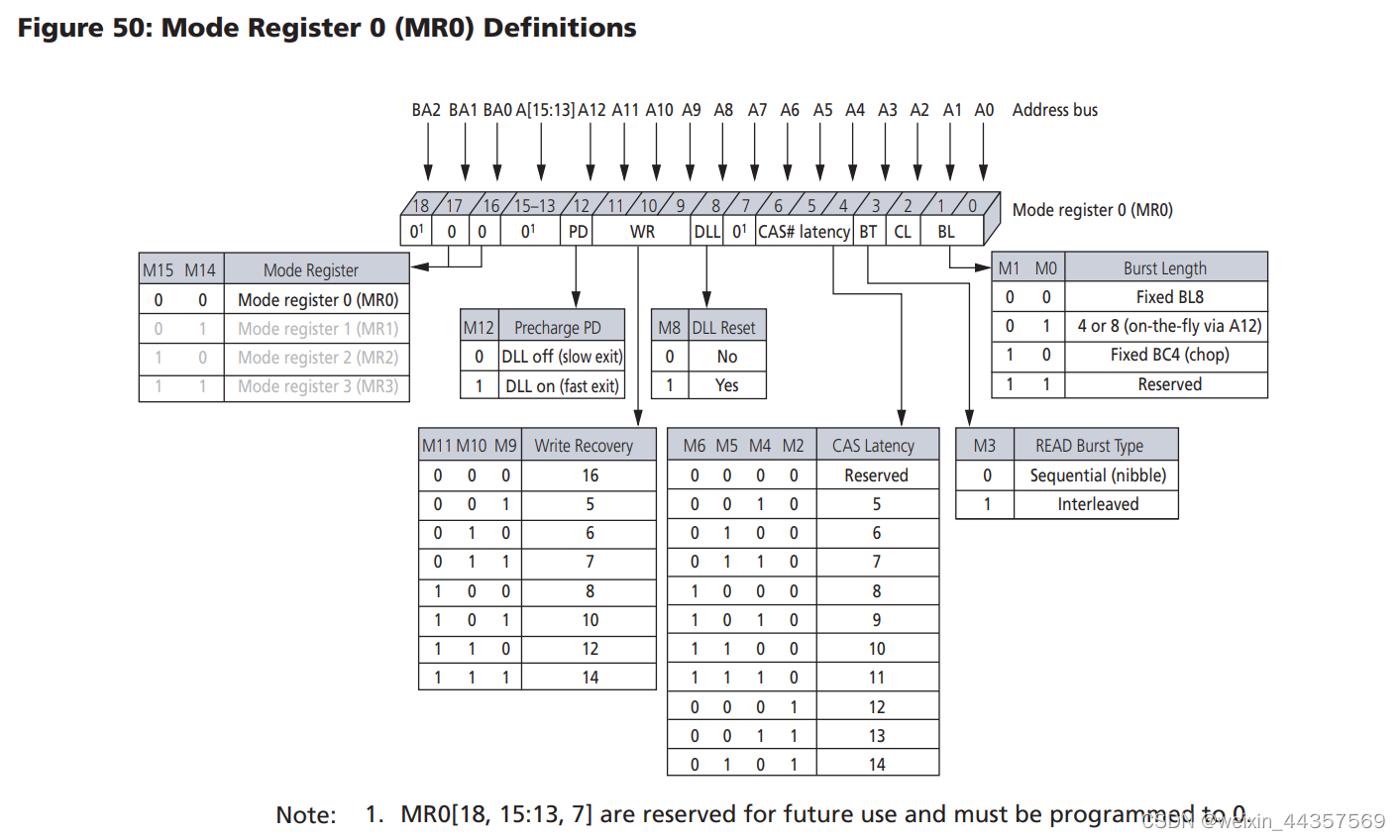

Burst Order即为低3位列地址 而Burst Type则由芯片的Mode Register0MR0来决定MR0具体说明如下图。

通常我们不需要关心MR0的设置通过设置列地址设置Burst Order为000即可此时突发读写均为顺序操作Cell空间。

五、容量计算

在了解地址构成与寻址方式后来计算芯片容量

8(bank) * 65536(row) * 128(column) * 128bit(mem cell) = 8Gbit

对应芯片型号MT41K512M16中

512(M) * 16(data width) = 8Gbit

512M即为8(bank) * 65536(row) * 128(column) * 8(burst length)为一颗芯片中可以操作的芯片IO数据位宽的数量。

因此MT41K2G4、MT41K1G8、MT41K512M16即为三种容量大小一致、数据位宽不同的SDRAM。

六、Vivado DDR3控制器MIG IP核

关于IP核的具体使用可以参考两位大佬的博客

Xilinx FPGA平台DDR3设计保姆式教程汇总篇——看这一篇就够了_子墨祭的博客-CSDN博客_fpga外接ddr3硬件设计方案![]() https://blog.csdn.net/m0_52840978/article/details/121191410快速上手Xilinx DDR3 IP核----汇总篇直达链接_孤独的单刀的博客-CSDN博客

https://blog.csdn.net/m0_52840978/article/details/121191410快速上手Xilinx DDR3 IP核----汇总篇直达链接_孤独的单刀的博客-CSDN博客![]() https://wuzhikai.blog.csdn.net/article/details/121841813我这里提两个小点

https://wuzhikai.blog.csdn.net/article/details/121841813我这里提两个小点

芯片选型

MT41K512M16芯片在MIG IP核中没有型号作为替代可以选择MT41K512M8作为替换MT41K512M16也是由两个MT41K512M8组成的仅需在选择数据位宽时选择正确的数据位宽即可。比如我的板卡连接了4片MT41K512M16组成64位宽的DDR3空间可以如下图选择。

接口信号

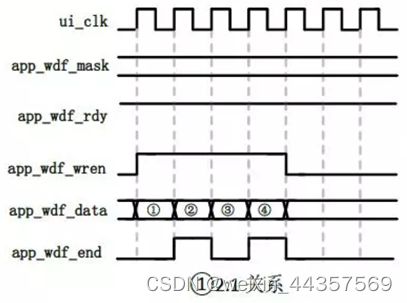

关于写DDR时MIG IP核的app_wdf_end信号设置该信号表示的是当前给控制器的是DDR突发写的最后一个数据。其与MIG IP核设置中的PHY时钟即芯片IO时钟和控制器时钟用户使用时钟比例的设置有关如下图所示芯片IO为上下沿同时传输数据控制器为单沿传输数据。芯片IO时钟设置较高时该比值仅支持4:1较低时可以选择4:1或2:1。

设置为4:1

- 用户从控制器收发的时钟与DDR内部存储单元核心时钟一致

- app_wdf_data为128(16*8)位与DDR内部存储单元BL=8的突发操作数据量一致

因此写DDR存储时每一个发送到控制器的有效数据app_wdf_data均为当前BL=8突发的第一个数据同时也是最后一个数据此时app_wdf_end 信号与app_wdf_wren信号同步如下图所示

设置为2:1

- 控制器工作时钟为DDR内部存储单元核心时钟的两倍

- 因为第一点为平衡数据传输量app_wdf_data变为64(16*4)位通过两次传输数据到控制器完成一次DDR内部存储单元核心所需的数据量也即 DDR内部存储单元BL=8的突发操作数据量16*8=128位

此时发送的第一个有效数据app_wdf_data为当前突发的前4个16位数据第二个数据app_wdf_data为当前突发的后4个16位数据因此此时app_wdf_end 信号应该在第二个数据时拉高与app_wdf_wren 信号关系如下图所示

app_wdf_***中wdf即为write data fifo

参考资料

DDR3 MIG 核中没有MT41K512M16**-107型号怎么处理 (xilinx.com)

DDR3 SDRAM IP 的写时序 | 电子创新网赛灵思社区 (eetrend.com)