Vivado综合属性之SRL

| 阿里云国内75折 回扣 微信号:monov8 |

| 阿里云国际,腾讯云国际,低至75折。AWS 93折 免费开户实名账号 代冲值 优惠多多 微信号:monov8 飞机:@monov6 |

本文介绍综合属性SRL_STYLE取register、srl、srl_reg、reg_srl、reg_srl_reg和block中的值时,对Schematic的影响。

SRL_STYLE用于指导Vivado将SRL(移位寄存器)映射为何种形式。

目录

默认值

测试代码

原理图

SRL_STYLE配置为register

测试代码

原理图

SRL_STYLE配置为srl

测试代码

原理图

对应的Device视图

资源利用率

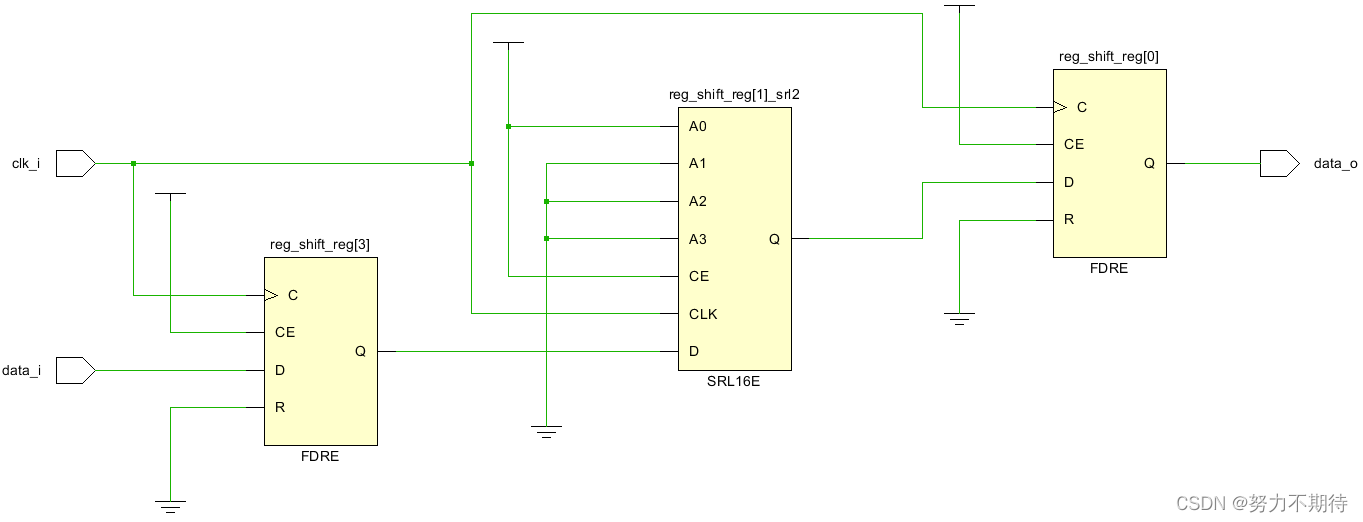

SRL_STYLE配置为srl_reg

测试代码

原理图

SRL_STYLE配置为reg_srl

测试代码

原理图

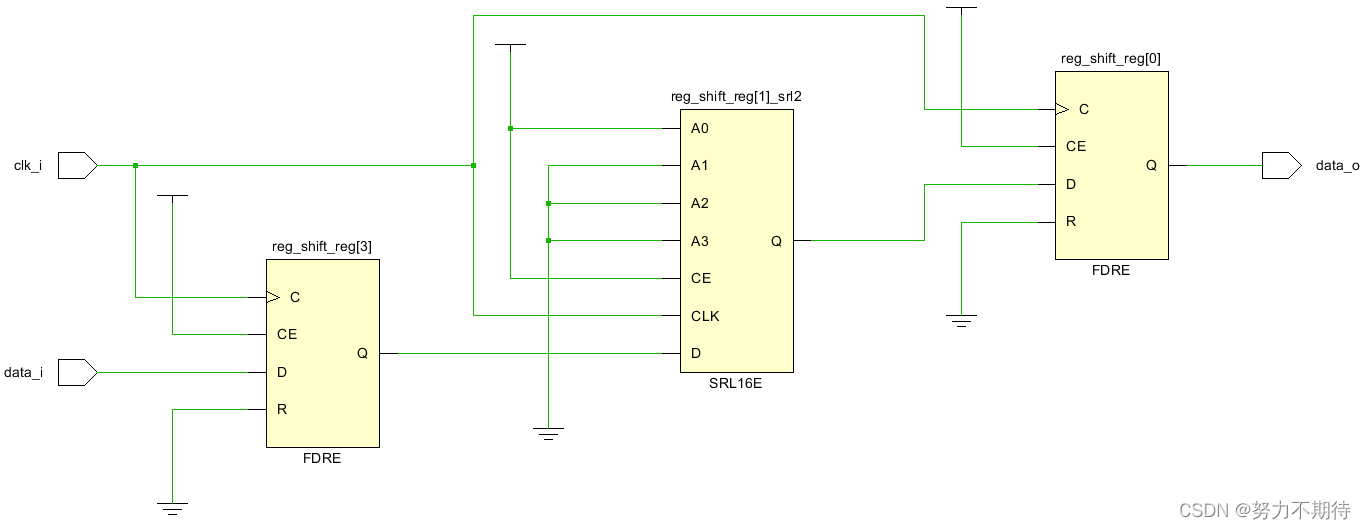

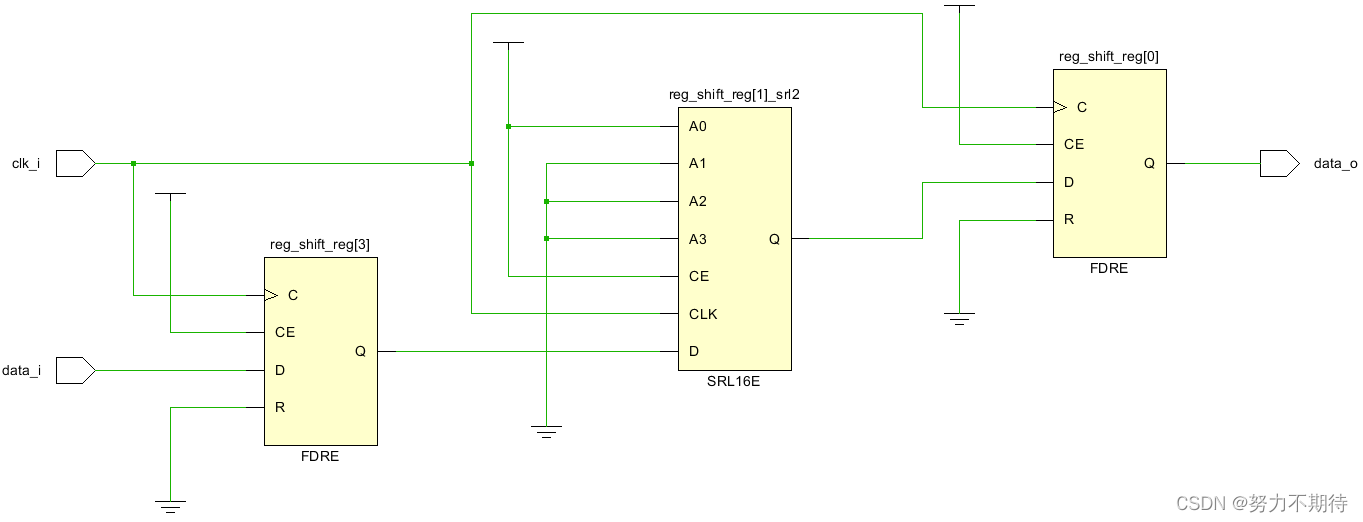

SRL_STYLE配置为reg_srl_reg

测试代码

原理图

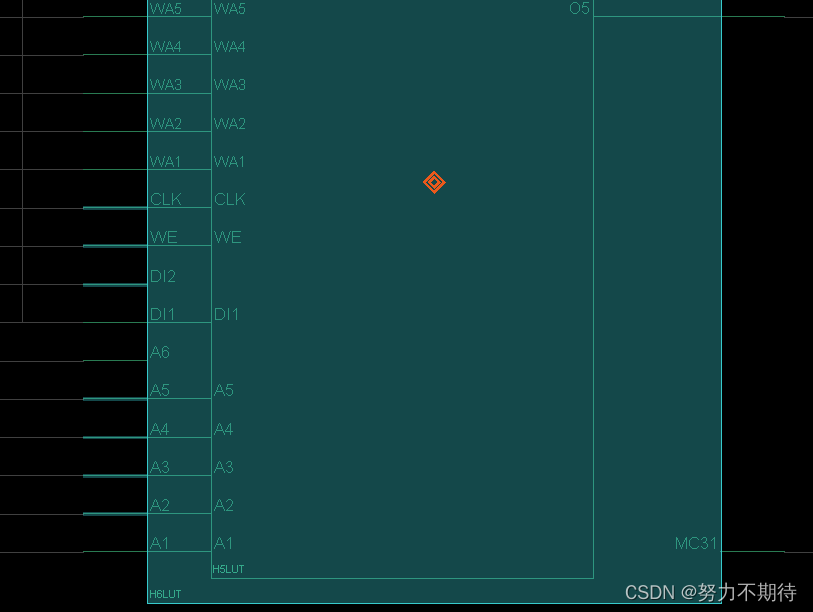

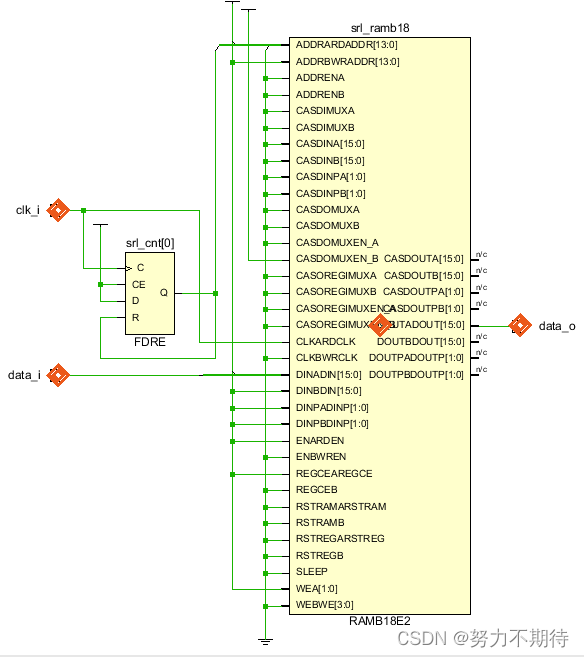

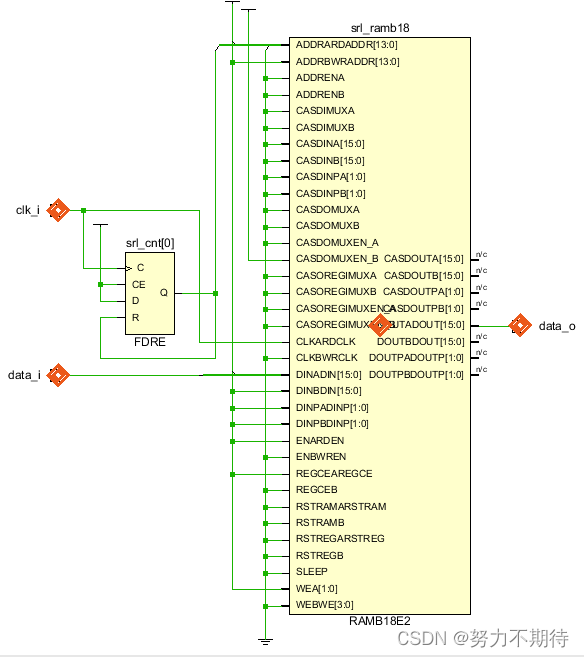

SRL_STYLE配置为block

测试代码

原理图

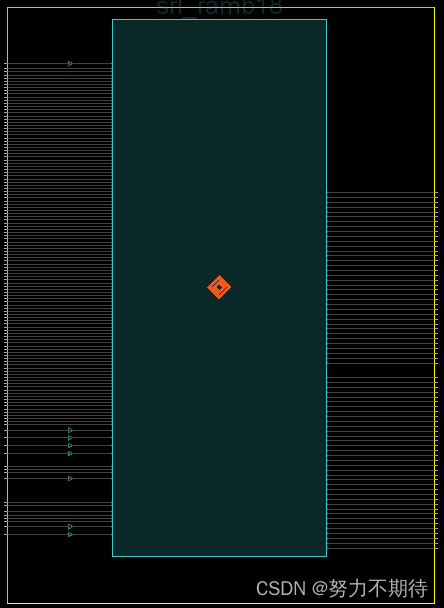

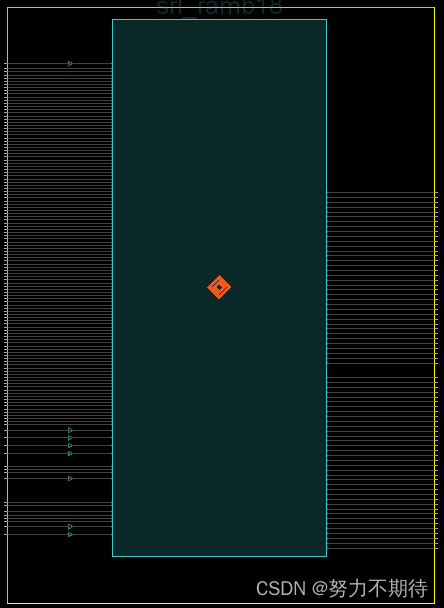

Device视图

资源利用率

默认值

测试代码

module top(

input clk_i,

input data_i,

output data_o);

parameter SHIFT = 4;

reg[SHIFT-1:0] reg_shift;

always @(posedge clk_i)

begin

reg_shift <={data_i,reg_shift[SHIFT-1:1]};

end

assign data_o = reg_shift[0];

endmodule

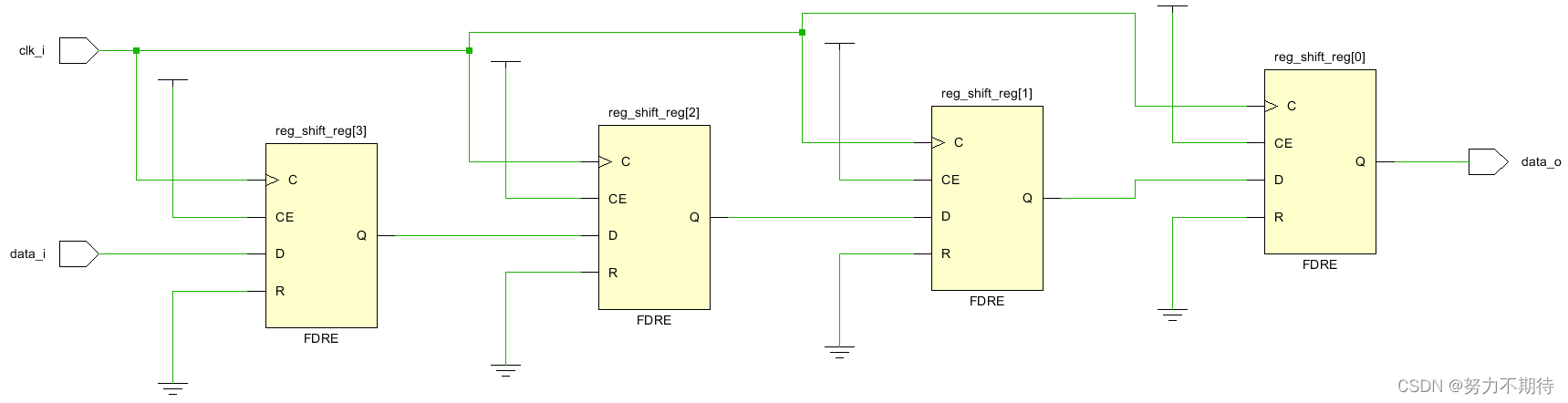

综合后的Schematic如下:

原理图

FDRE表示一个单D型触发器。

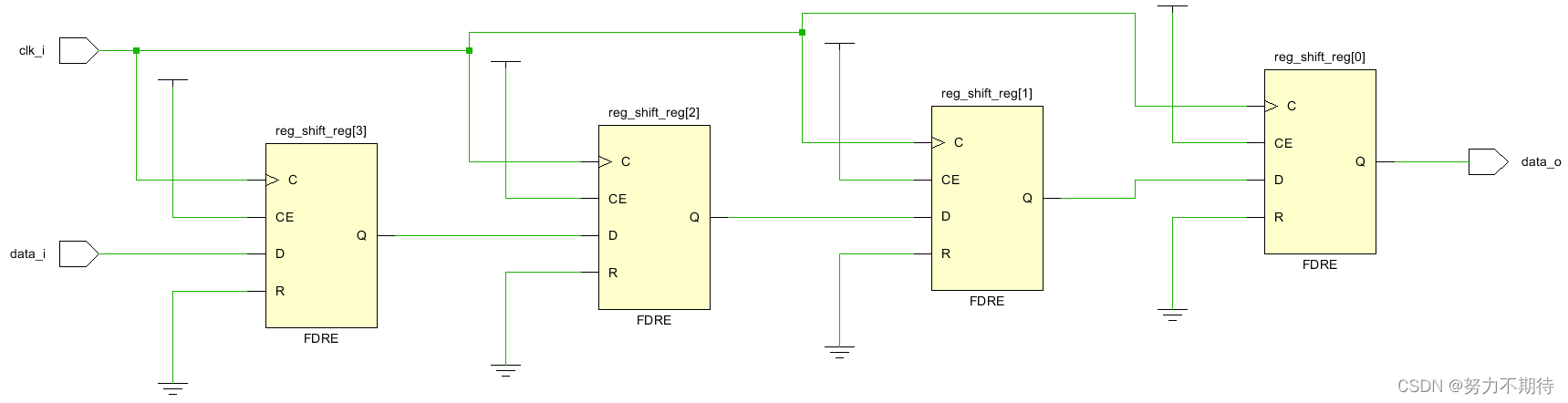

SRL_STYLE配置为register

用FF(Flip Flop,触发器)生成SRL。

测试代码

module top(

input clk_i,

input data_i,

output data_o);

parameter SHIFT = 4;

(*srl_style = "register"*) reg[SHIFT-1:0] reg_shift;

always @(posedge clk_i)

begin

reg_shift <={data_i,reg_shift[SHIFT-1:1]};

end

assign data_o = reg_shift[0];

endmodule

原理图

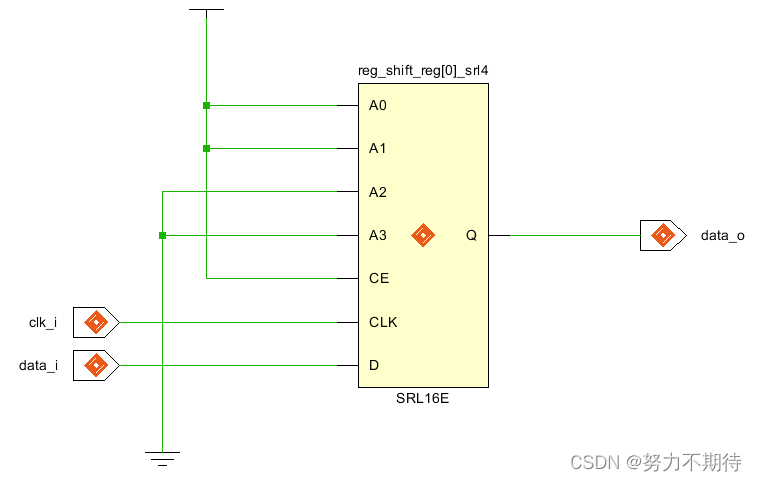

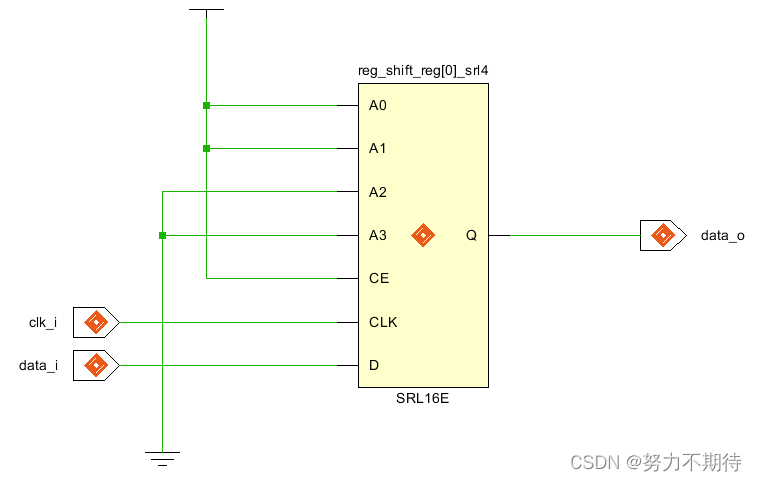

SRL_STYLE配置为srl

用LUT生成SRL。

测试代码

module top(

input clk_i,

input data_i,

output data_o);

parameter SHIFT = 4;

(*srl_style = "srl"*) reg[SHIFT-1:0] reg_shift;

always @(posedge clk_i)

begin

reg_shift <={data_i,reg_shift[SHIFT-1:1]};

end

assign data_o = reg_shift[0];

endmodule

原理图

SRL16E表示一个可以最大实现16位移位寄存的移位寄存器。

对应的Device视图

红色大框框表示一个SLICEM,红色MARK对应上上图的SRL16E,上图将红色MARK部分放大,可以看出SRL16E其实是LUT构成的,见下图。

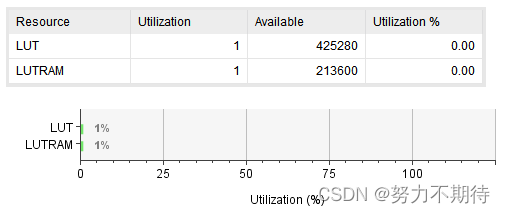

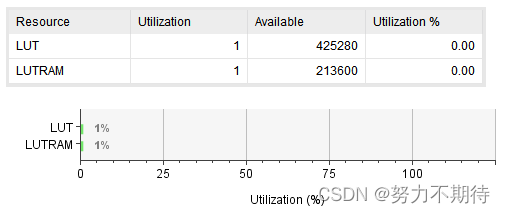

资源利用率

资源利用率报告中的LUT是指设计中消耗的所有LUT,包括SLICEL中的LUT和SLICEM中的LUT。

资源利用率报告中的LUTRAM是指设计中消耗的SLICEM中的LUT。

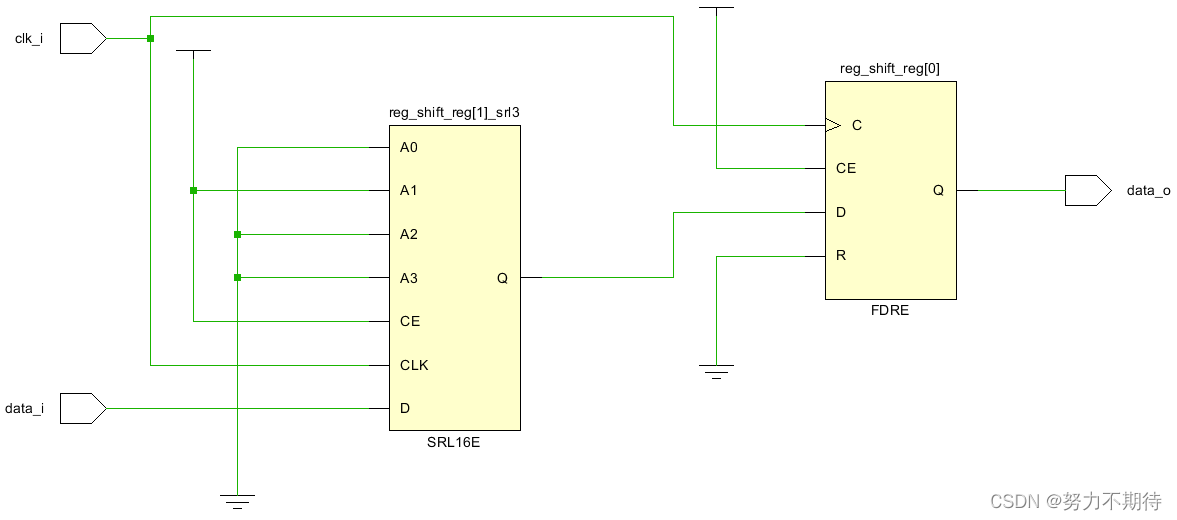

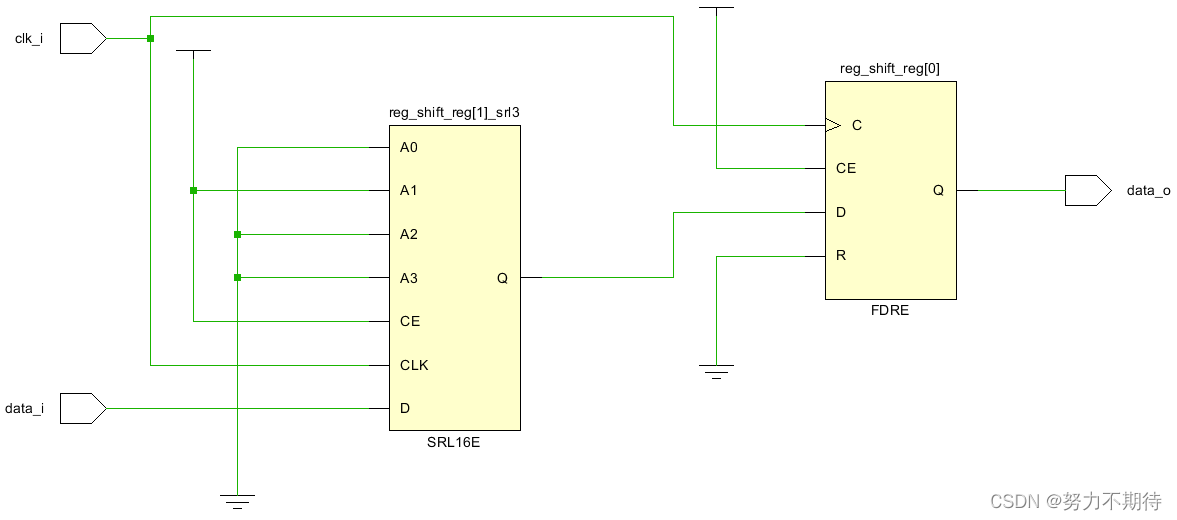

SRL_STYLE配置为srl_reg

用LUT和FF(Flip Flop,触发器)生成SRL,最后一级深度用FF。

测试代码

module top(

input clk_i,

input data_i,

output data_o);

parameter SHIFT = 4;

(*srl_style = "srl_reg"*) reg[SHIFT-1:0] reg_shift;

always @(posedge clk_i)

begin

reg_shift <={data_i,reg_shift[SHIFT-1:1]};

end

assign data_o = reg_shift[0];

endmodule

原理图

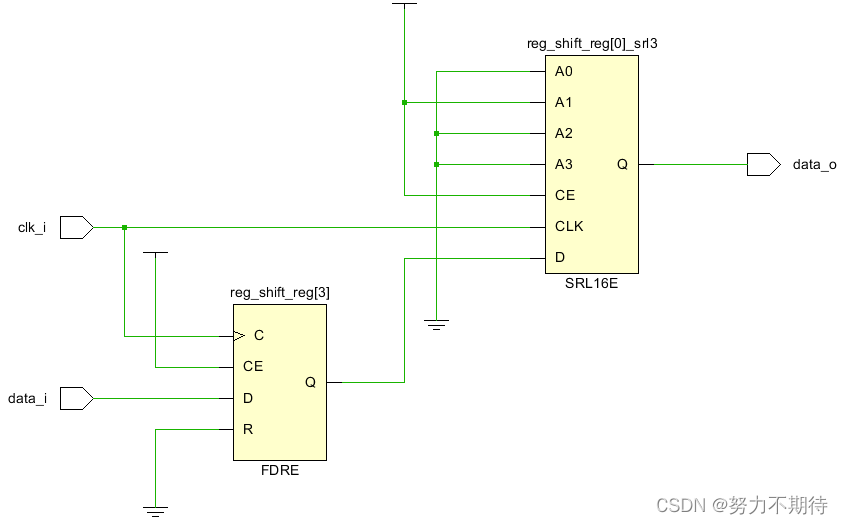

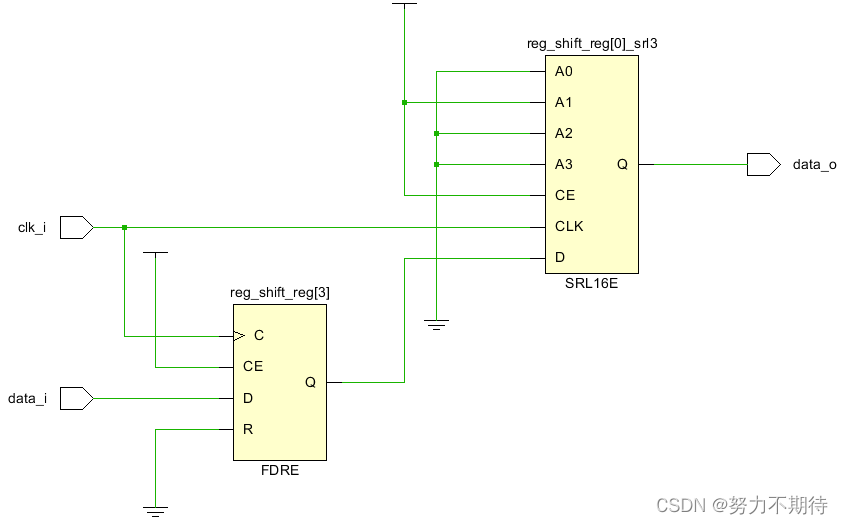

SRL_STYLE配置为reg_srl

第一级深度用FF(Flip Flop,触发器),其他用LUT。

测试代码

module top(

input clk_i,

input data_i,

output data_o);

parameter SHIFT = 4;

(*srl_style = "reg_srl"*) reg[SHIFT-1:0] reg_shift;

always @(posedge clk_i)

begin

reg_shift <={data_i,reg_shift[SHIFT-1:1]};

end

assign data_o = reg_shift[0];

endmodule

原理图

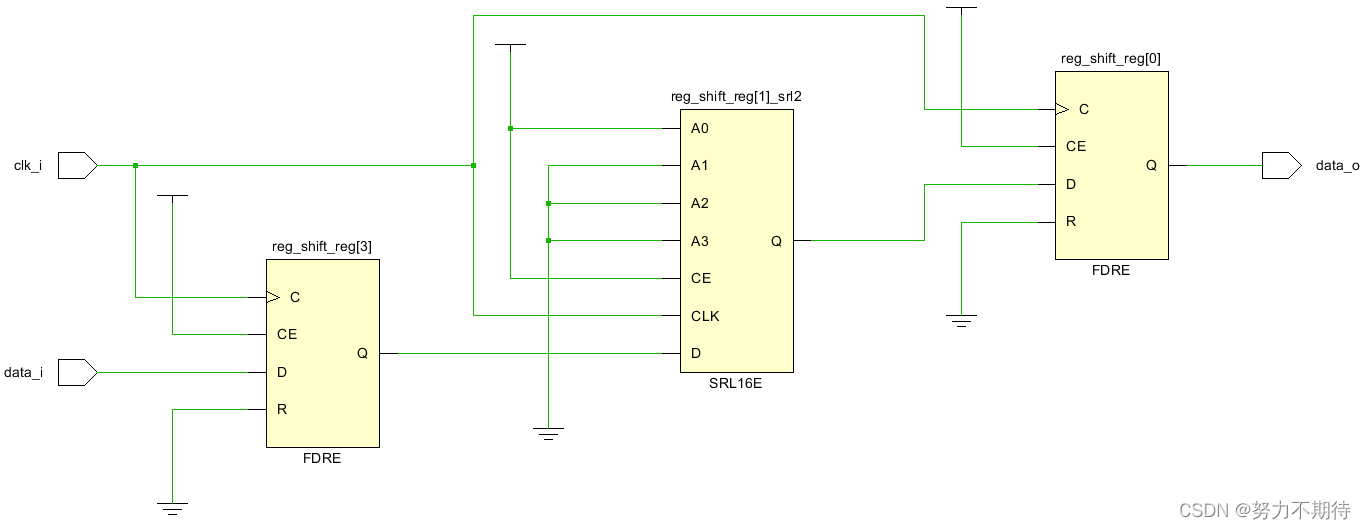

SRL_STYLE配置为reg_srl_reg

第一和最后一级深度用FF(Flip Flop,触发器),其他用LUT。

测试代码

module top(

input clk_i,

input data_i,

output data_o);

parameter SHIFT = 4;

(*srl_style = "reg_srl_reg"*) reg[SHIFT-1:0] reg_shift;

always @(posedge clk_i)

begin

reg_shift <={data_i,reg_shift[SHIFT-1:1]};

end

assign data_o = reg_shift[0];

endmodule

原理图

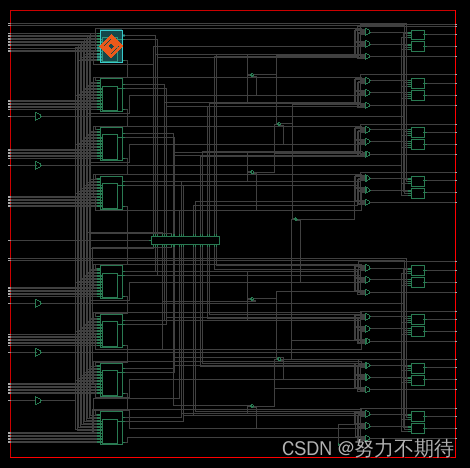

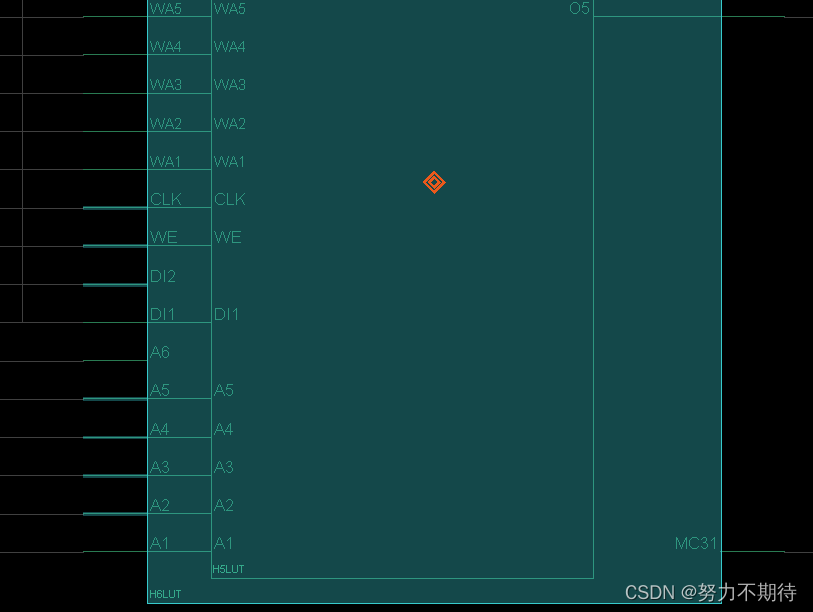

SRL_STYLE配置为block

用BRAM生成SRL。

测试代码

module top(

input clk_i,

input data_i,

output data_o);

parameter SHIFT = 4;

(*srl_style = "block"*) reg[SHIFT-1:0] reg_shift;

always @(posedge clk_i)

begin

reg_shift <={data_i,reg_shift[SHIFT-1:1]};

end

assign data_o = reg_shift[0];

endmodule

原理图

RAMB18E2表示UltraScale系列FPGA(我的环境是XCZU21DR)使用Block RAM构成的18Kb 存储单元。

Device视图

黄色框框表示1个Block RAM。

资源利用率

| 阿里云国内75折 回扣 微信号:monov8 |

| 阿里云国际,腾讯云国际,低至75折。AWS 93折 免费开户实名账号 代冲值 优惠多多 微信号:monov8 飞机:@monov6 |