[HDLBits] Exams/m2014 q6-CSDN博客

| 阿里云国内75折 回扣 微信号:monov8 |

| 阿里云国际,腾讯云国际,低至75折。AWS 93折 免费开户实名账号 代冲值 优惠多多 微信号:monov8 飞机:@monov6 |

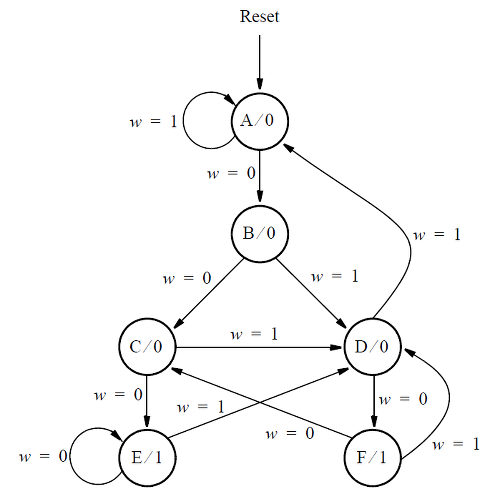

Consider the state machine shown below, which has one input w and one output z.

Implement the state machine. (This part wasn't on the midterm, but coding up FSMs is good practice).

module top_module (

input clk,

input reset, // synchronous reset

input w,

output z);

parameter a=3'b000,b=3'b001,c=3'b010,d=3'b011,e=3'b100,f=3'b101;

reg [2:0] state,next;

always@(*) begin

case(state)

a:next<=w?a:b;

b:next<=w?d:c;

c:next<=w?d:e;

d:next<=w?a:f;

e:next<=w?d:e;

f:next<=w?d:c;

endcase

end

always@(posedge clk) begin

if(reset)

state<=a;

else

state<=next;

end

assign z=(state==e)||(state==f);

endmodule