基于FPGA的数字电子钟的设计与实现-实验报告

| 阿里云国内75折 回扣 微信号:monov8 |

| 阿里云国际,腾讯云国际,低至75折。AWS 93折 免费开户实名账号 代冲值 优惠多多 微信号:monov8 飞机:@monov6 |

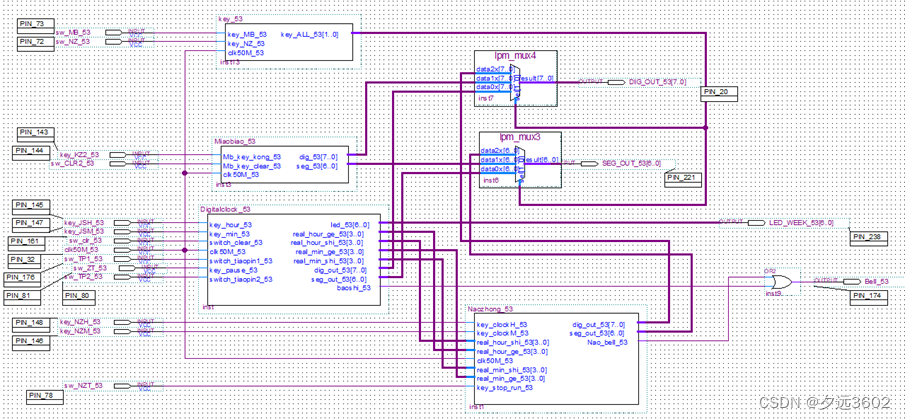

- 系统顶层模块设计

图1 系统顶层设计电路

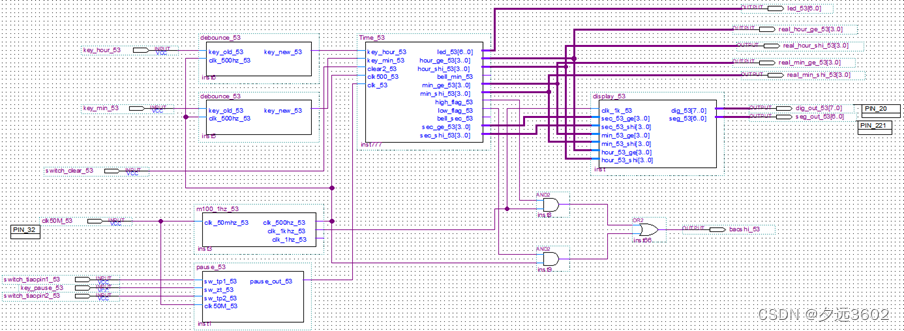

图2 数字钟功能设计电路

图3 秒表功能设计电路

图4 闹钟功能设计电路

1.1系统功能

该系统分为数字钟、秒表、闹钟三个功能模块通过开关控制模块key_53,可以用两个开关控制秒表和闹钟的使用及设置界面(初始化为数字钟使用及设置界面)。数字钟的功能包括秒、分钟、小时的计时、奇数秒整点报时、以及星期显示并将计数结果清晰稳定地显示到8位数码管上格式为“xx时-xx分-xx秒”其中数字6和9为补段后的显示效果,并可以通过开关控制数字钟的暂停、清零以及调频功能通过按键进行数字钟小时、分钟的校时在计时为“xx:59:51-xx:59:59”时在奇数秒报时前4次以500Hz报时最后一次为1khz同时通过7个LED灯显示星期数。秒表的功能包括开始、暂停、清零通过按键控制。闹钟的功能包括闹钟小时、分钟设置以及闹钟铃声的停止。

基本功能秒、分钟、小时的计数及进位。

拓展功能数字钟调频、暂停、清零、奇数秒不同频率整点报时、校时、星期显示、八位数码管显示、69补段秒表开始、暂停、清零闹钟设置、停止。

1.2设计思路

分别设计好数字钟、秒表、闹钟三个模块的功能然后将其封装再设计一个开关模块控制LPM_MUX三选一数据选择器选择三个模块的输出作为总输出使其清晰稳定地显示到8位数码管上。下面分别概述数字钟、秒表、闹钟的设计思路。

数字钟数字钟的时、分、秒计时功能可以用74390芯片设计模60、模24计数器并封装实现计时和进位功能调频、暂停功能可用74151芯片进行1Hz、500Hz、1000Hz的选择暂停则不选择输入信号清零功能通过开关经过消抖装置连入秒、分、时的清零端实现清零利用参数译码器LPM_DECODE组成整点报时模块与蜂鸣器相连即可实现整点前奇数秒报时的功能将key2key3经过消抖装置分别与分、秒进位信号相或以后输入时、分的信号端实现手动校时的功能。

秒表用74390芯片设计模10、模60和模100计数器用模60实现秒、分钟的计数输入1kHz信号经过模10计数器之后进位信号连接模100的信号输入模块temp_53temp_53模块用74151设计按键输入连接消抖模块后作为temp_53模块的输入实现秒表的开始和暂停功能清零功能通过开关经过消抖装置连接模60、模100的清零端实现秒表清零。

闹钟闹钟模块包括设置闹钟时间的set_Naozhong模块和比较闹钟设置时间与数字钟时间是否相同的compare_53模块。设置闹钟时间模块包含模60和模24计数器按键输入连接消抖模块后作为模60和模24的信号输入从而达到设置小时、分钟的功能compare_53模块用7485数值比较器比较闹钟设置时间与数字钟时间是否相同输出作为闹铃信号从而达到闹钟功能。

- 分频模块电路设计及仿真

- 模块功能

对50mHz的时钟信号分频输出1Hz的秒时钟、500Hz和1kHz的扫描时钟。

- 设计思路

利用74390芯片实现模2、5、10、100的计数功能将50mHz的信号经过两次m100的分频后得到5kHz的时钟信号接入74390的1CLKB端该计数器以5421BCD码进行模十计数通过1QA输出得到500Hz信号1QD输出得到1kHz信号将1QA接入2CLKB端通过模5计数器进行5分频后再通过一个m100分频即可得到1Hz信号。

- 设计结果电路

图5 分频功能电路

- 测试结果

图6 m100波型仿真

- 计时模块设计及仿真

- 分、秒计时模块

- 模块功能

实现模60计数的功能1QD-1QA为个位上二进制数的输出2QD-2QA为十位上二进制数的输出当计数满60时清零输出进位信号同时设置clr信号和报时信号报时模块介绍当clr信号为1时清零。

- 设计思路

利用74390芯片实现模100计数器时钟信号接入1CLKA端1QA连接1CLKB1QD连接2CLKA2QA连接2CLKB1QD-1QA为个位上二进制数的输出2QD-2QA为十位上二进制数的输出当个位为0000十位为0110时清零实现模60计数的功能74390芯片清零端高电平有效故将十位的2QB和2QC相与后接一个输出端作为进位信号输出再将清零信号与清零按钮输入端相或后接入1CLR和2CLR实现当两者其中一个为1时立即清零的功能。最后将1QD-1QA和2QD-2QA分别对应接输出端ge_53[3..0]和shi_53[3..0]同时从输出端用与操作输出报时信号。

- 设计结果

图7 模60设计电路

- 仿真测试

图8 模60波形仿真

-

- 小时计时模块

- 模块功能

实现模24计数的功能1QD-1QA为个位上二进制数的输出2QD-2QA为十位上二进制数的输出当计数满24时清零输出进位信号(用于显示星期)同时输出clr信号当clr信号为1时清零。

- 设计思路

利用74390芯片实现模24计数器时钟信号接入1CLKA端1QA连接1CLKB1QD连接2CLKA2QA连接2CLKB1QD-1QA为个位上二进制数的输出2QD-2QA为十位上二进制数的输出当个位为0100十位为0010时清零实现模24计数的功能74390芯片清零端高电平有效故将十位的2QB和个位的1QC相与后接一个输出端作为进位信号输出再将清零信号与清零按钮输入端相或后接入1CLR和2CLR实现当两者其中一个为1时立即清零的功能。最后将1QD-1QA和2QD-2QA分别对应接输出端ge_53[3..0]和shi_53[3..0]。

- 设计结果

图9 模24设计电路

- 仿真测试

图10 模24波形仿真

- 数码管动态显示模块

- 动态显示模块的设计

图11 动态显示模块功能框图

-

- 扫描模块cnt8

- 模块功能

产生dig_select和code_select模块所需要的地址信息扫描时钟决定位选信号和数据切换的速度。(为满足后续八位数码管显示功能这里将cnt6模块改为cnt8模块)

- 设计思路

使用74390芯片将1QD连入1CLR端实现模8的功能。

- 设计结果电路

图12 扫描模块cnt8设计电路

- 仿真测试

图13 扫描模块cnt8波形仿真

-

- 位选模块dig_select

- 模块功能

在地址端的控制下产生位选信号。

- 设计思路

选用74138三线-八线译码器输入信号为vcc的高电平当位选的信号输入时输出对应的位选变为高电平使该输出位对应的一位数码管工作。在输入信号时要保证位选信号实现000-111循环从而让对应的8位数码管依次循环进入工作状态利用视觉暂留达到八位数码管显示的结果。

- 设计结果

图14 dig_select设计电路

- 仿真测试

图15 dig_select波形仿真

-

- 数据选择模块code_select

- 模块功能

输入 6 组数据每组数据 4bit本模块完成在地址端的控制下从 6 组数据当中选择 1 组输出。

- 设计思路

利用74151数据选择器从八组数据中的第0、1、2、3位中选择一个作为该位的输出。

- 设计结果

图16 code_select设计电路

- 仿真测试

图17 code_select波形仿真

-

- 译码模块decoder

- 模块功能

将输入的4位8421BCD码译为七段码使数码管以十进制数子的形式显示数字同时利用基本逻辑门进行69补段功能的实现。

- 设计思路

因7448对“6”“9”输出不符合日常认知故将其输出补全补全后功能被如下。

| D | C | B | A | Qa | Qb | Qc | Qd | Qe | Qf | Qg | 字形 |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 2 |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 3 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 4 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 5 |

| 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 6 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 7 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 8 |

| 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 9 |

表1 补全“6”“9”后7448功能表

- 设计结果

图18 decoder设计电路

- 仿真测试

图19 decoder波形仿真

-

- 动态显示模块电路图

图20 动态显示模块dispay设计电路

输入1Hz信号经过模8计数器输出四位二进制码信号利用视觉暂留效果通过dig_select模块产生位选输出code_select在输入时、分、秒的个、十位信号后输出段选的二进制码最后通过decoder模块产生段选输出。

通过实验观察结果符合预期因此方案设计正确。

- 其他扩展功能

- 调频功能

- 模块功能

通过拨动sw3sw2sw1来控制计时速度。当sw3sw2sw1=000时输入1Hz信号当sw3sw2sw1=001时输入500Hz信号当sw3sw2sw1=010时输入1kHz信号。

- 设计思路

选用74151芯片三个开关经过消抖后连接输入段1Hz、500Hz、1kHz连接D0、D1、D2从而通过开关实现选频。

- 设计结果

图21 调频功能设计电路

- 仿真测试

图22 m100波形仿真

-

- 暂停

- 模块功能

通过开关sw3控制闹钟的暂停和开始。

2 设计思路

选用74151芯片开关经过消抖后连接输入段1Hz连接D0开关sw3连接高位C这样拨码开关上拨则选择输出D4即无脉冲输出从而达到暂停效果。由于暂停和调频设计思路大致相同这里将调频和暂停一起封装为一个模块方便调用。

- 设计结果

图23 暂停模块设计电路

- 仿真测试

由于总输入频率50mHz过大这里进行m100仿真。

图24 m100模块波形仿真

-

- 清零

1 模块功能

通过开关sw0实现清零当sw为逻辑1时数字钟清零为逻辑0时数字钟恢复计时功能。

- 设计思路

对各个计数模块添加一个外界输入信号当信号为1时实现清零计数功能该信号与原计数模块进位信号相或接入清零端从而实现手动清零功能。

3 设计结果

图25 小时清零模块设计电路

图26 分钟清零模块设计电路

图27 清零模块设计电路

4 仿真测试

图28 小时清零模块波形仿真

图29 分钟清零模块波形仿真

-

- 校时功能

- 模块功能

按键k1、k2从而实现分钟、小时数+1。

- 设计思路

Key2和分钟的进位信号相或后连接至时钟的进位模块Key1和秒钟的进位进行相或后连接至分钟的进位模块。

- 设计结果

图30 校时功能设计电路

-

- 整点报时

1 模块功能

在计时为“xx:59:51-xx:59:59”时奇数秒报时前4次以500Hz报时最后一次为1kHz。

设计思路

2 设计思路

利用参数译码器LPM_DECODE组成整点报时模块控制秒、分计时的模块对报时模块进行秒、分钟的个位和十位的参数输入满足分钟为59秒为51-59计数时输出信号前四次输出为500hz闹铃信号最后一次为1kHz信号。

3 设计结果

图31 整点报时设计电路

- 仿真测试

图32 整点报时波形仿真

-

- 69补段

69补段在decoder模块的介绍中已进行设计功能、思路分析和波形仿真这里不在赘叙。

-

- 八位显示分隔符-

- 模块功能

在八位数码管上的时、分、秒之间加上一个横杠。

- 设计思路

要加上两个-故设计cnt8扫描8个数码管使其能按要求同时显示不同的数值。我们可以观察到当DCBA为1111时decoder译码器的输出刚好为0000000所以让数据选择模块中每片74151的D2D5都接1再对decoder改动一下可以使得当DCBA为1111时输出为0000001,即可以实现加两条横杠的功能。

- 设计结果

前述cnt8、decoder、dig_select、code_select模块已展示过设计电路图这里不再赘述。

- 仿真测试

前述cnt8、decoder、dig_select、code_select模块已展示过波形仿真图这里不再赘述。

-

- 星期显示

- 模块功能

用led灯记录星期小时计时满24进位星期一则led0亮星期二则led1亮依此类推。

- 设计思路

要满足星期显示这里我们选用74390芯片设计模7计数器其中小时计满24小时后向模7计数器进位进行7进制计数并输出此时对应的计数结果。

- 设计结果

图33 星期显示设计电路

图34 模7设计电路

图35 led模块设计电路

- 仿真测试

图36 模7波形仿真

图37 led模块波形仿真

-

- 秒表功能

1 模块功能

通过按键k3实现秒表的计时开始、暂停按键k4实现秒表的清零

2 设计思路

根据前述数字钟设计的启发考虑到秒表计时的小数位这里我们输入1kHz信号将其先接入一个模10分频为100Hz信号0.01s再接入一个模100和两个模60计数由数字电路与逻辑设计理论课的启发开始暂停选用JK触发器接高电平vcc实现。

3 设计结果

图38 秒表总模块设计电路

图39 秒表计时模块设计电路

图40 秒表开关模块设计电路

4 仿真测试

考虑到输入信号50mHz、1kHz等数值过大这里进行模100模块的波形仿真。

图41 模100波形仿真

-

- 闹钟功能

1 模块功能

通过按键k5、k6设置闹钟时间当数字钟到大与闹钟相同时间后响铃通过k7通知闹钟响铃声音的关闭。

2 设计思路

由设计数字钟时的灵感参考数字钟校时电路将开关分别与分钟的进位信号相或后连接至时钟的进位模块、与秒钟的进位进行相或后连接至分钟的进位模块从而达到设置时间的功能然后通过compare模块比较数字钟时间与闹钟时间是否相同。compare模块选用7485数值比较器分别比较时、分的个、十位二进制代码从而达到比较闹钟设置时间与数字钟时间是否相同的功能若相同则输出逻辑1实现响铃持续一分钟否则输出逻辑0。

3 设计结果

图42 闹钟总模块电路

图43 闹钟时间设置模块电路

图44 闹钟总比较模块compare设计电路

图45 闹钟时、分每一位二进制码比较模块small_compare设计电路

- 系统总体测试

系统总体测试结果如“附件一 评分细则及测试原始数据记录”。

- 系统设计实现过程中遇到的主要问题、解决思路和解决方案

7.1闹钟设置时间与数字钟时间比较模块compare_53的设计

- 主要问题

在进行这一模块设计时刚开始对两个时间的比较没有头绪无从下手。

- 解决思路

用百度查阅相关资料了解数值比较器7485后我便打开了思路用数据比较设置时间与数字钟时间的小时和分钟是否相同若相同则输出闹钟信号实现闹钟响铃。

- 解决方案

用7485芯片设计一个四位数值比较器并封装然后将小时、分钟各自的个、十位二进制码分别进行比较全部相同则输出逻辑1。

7.2数码管显示

- 主要问题

当进行秒表、闹钟功能的使用时disply模块只能输出一组dig和seg信号。

- 解决思路

采用LPM_MUX进行数字钟、秒表、闹钟的deg、seg信号选择输出。

- 解决方案

将数字钟、秒表、闹钟分别封装然后设计一个开关控制模块key_53连接LPM_MUX,对其各自的deg、seg信号进行选择输出(具体设计见顶层电路图)。

- 心得体会

本实验仅供参考请勿抄袭。

图46 数电实验回忆