FPGA知识汇集-FPGA系统时序理论

| 阿里云国内75折 回扣 微信号:monov8 |

| 阿里云国际,腾讯云国际,低至75折。AWS 93折 免费开户实名账号 代冲值 优惠多多 微信号:monov8 飞机:@monov6 |

时序约束条件

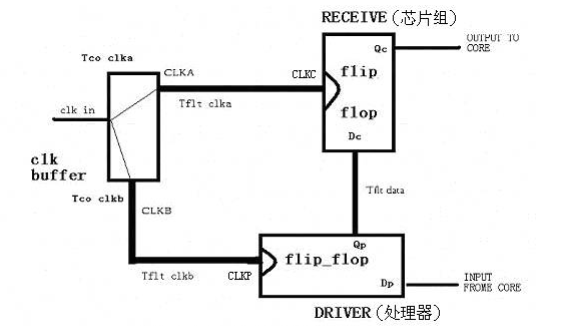

下面来具体讨论一下系统时序需要满足的一些基本条件。我们仍然以下图的结构为例并可以据此画出相应的时序分析示意图。

在上面的时序图中存在两个时序环我们称实线的环为建立时间环而虚线的环我们称之为保持时间环。可以看到这两个环都不是闭合的缺口的大小就代表了时序裕量的多少因此设计者总希望尽可能增大这个缺口。同时还要注意到每个环上的箭头方向不是一致的而是朝着正反两个方向因为整个系统时序是以时钟上升沿为基准的所以我们时序环的起点为系统时钟clk in的上升沿而所有箭头最终指向接收端的控制时钟CLKC的边沿。

先来分析建立时间环

缺口的左边的半个时序环代表了从第一个系统时钟上升沿开始直到数据传输至接收端的总的延时我们计为数据延时以Tdata_tot表示

Tdata_tot=Tco_clkb+Tflt_clkb +Tco_data +Tflt_data

上式中Tco_clkb是系统时钟信号CLKB在时钟驱动器的内部延迟Tflt_ clkb 是CLKB从时钟驱动器输出后到达发送端CPU触发器的飞行时间Tco_data是数据在发送端的内部延迟Tflt_data是数据从发送端输出到接收端的飞行时间。

从CLKC时钟边沿的右边半个时序环代表了系统时钟到达接收端的总的沿时我们计为时钟延时以Tclk_tot表示

Tclk_tot =Tcycle +Tco_clka +Tflt_clka – Tjitter

其中Tcycle是时钟信号周期Tco_clka 是系统时钟信号CLKA第二个上升沿在时钟驱动器的内部延迟Tflt_clka是时钟信号从时钟驱动器输出到达接收端触发器的飞行时间Tjitter是时钟的抖动误差。

因此我们可以根据建立时间裕量的定义得到

Tsetup_margin = Tclk_tot – Tdata tot – Tsetup

将前面的相应等式带入可得

Tsetup_magrin = Tcycle + Tco_clka + Tflt_clka – Tjitter – Tco_clkb – Tflt_clkb – Tco_data – Tflt_data – Tsetup

我们定义时钟驱动器(PLL)的两个时钟输出之间的偏移为Tclock_Skew 两根CLOCK走线之间的时钟偏移为TPCB_Skew 即

Tclock_Skew = Tco_clkb - Tco_clka

TPCB_Skew = Tflt_clkb - Tflt_clka

这样就可以得到建立时间裕量的标准计算公式

Tsetup_magrin =Tcycle – TPCB_skew –Tclock_skew –Tjitter – Tco_ data -Tflt_data-Tsetup 1.6.1

再来看保持时间环

对照上图我们可以同样的进行分析

Tdata_delay = Tco_clkb + Tflt_clkb + Tco_data + Tflt_data

Tclock delay = Tco_clka + Tflt_clka

于是可以得出保持时间裕量的计算公式

Thold margin = Tdata_delay – Tclock_dalay – Thold_time

即: Thold margin = Tco_data + Tflt_data + Tclock_skew + Tpcb_skew – Thold 1.6.2

可以看到式1.6.2中不包含时钟抖动Jitter的参数。这是因为Jitter是指时钟周期间Cycle to Cycle的误差而保持时间的计算和时钟周期无关。

对于任何时钟控制系统如果要能保证正常工作就必须使建立时间余量和保持时间裕量都至少大于零即Tsetup marin >0Thold margin >0将公式1.6.1和1.6.2分别带入就可以得到普通时钟系统的时序约束条件不等式

TPCB_skew +Tclock_skew +Tjitter + Tco_data + Tflt_data+Tsetup< Tcycle (1.6.3)

Tco_data + Tflt_data + Tclock_skew + Tpcb_skew > Thold (1.6.4)

需要注意的是

1. 数据在发送端的内部延时Tco_data可以从芯片的datasheet查到这个值是一个范围在式1.6.3中取最大值在式1.6.4中取最小值。

2.数据在传输线上的飞行时间Tflt_data在实际计算中应该取最大/最小飞行时间参数在式1.6.3中取最大飞行时间在式1.6.4中取最小飞行时间。

3. 时钟的偏移TPCB_skew和Tclock_skew也是一个变化的不确定参数一般为+/-N ps同样在建立时间约束条件1.6.3中取+Nps而在保持时间约束条件1.6.4中取-Nps。

从上面的分析可以看到对于PCB设计工程师来说保证足够稳定的系统时序最有效的途径就是尽量减小PCB skew和信号传输的飞行时间而其它的参数都只和芯片本身的性能有关。实际中经常采取的措施就是严格控制时钟和数据的走线长度调整合理的拓补结构并尽可能减少信号完整性带来的影响。然而即便我们已经考虑的很周全普通时钟系统的本身的设计瓶颈始终是无法打破的也就是建立时间的约束我们在尽可能减少由PCB布线引起的信号延迟之外器件本身的特性如Tco、Jitter、TSetup等等将成为最主要的制约因素尽管我们可以通过提高工艺水平和电路设计技术来不断提高数字器件的性能但得到的效果也仅仅是在一定范围之内提升了系统的主频在频率超过300MHz的情况下我们将不得不放弃使用这种普通时钟系统设计。

那么应该怎么解决普通时钟系统的瓶颈呢且听下回分解。

更多有趣的话题请看链接

FPGA知识汇集-编写可综合代码(RTL)需要注意的规则总结

FPGA知识汇集-串行 RapidIO: 高性能嵌入式互连技术