STM32-RCC时钟-时钟树介绍

| 阿里云国内75折 回扣 微信号:monov8 |

| 阿里云国际,腾讯云国际,低至75折。AWS 93折 免费开户实名账号 代冲值 优惠多多 微信号:monov8 飞机:@monov6 |

本篇文章主要讲解STM32的时钟部分解读时钟树。本片文章较长请耐心看完。那么你会了解对于STM32的一切时钟的来龙去脉。且本片文章大量的对照着STM32Fxx手册。请读者们提前下好手册的链接我放这了

STM32的手册STM32FXX手册 https://pan.baidu.com/s/1sk1_DSbL5ZV33I7zqzJEsg

提取码pyj1

目录

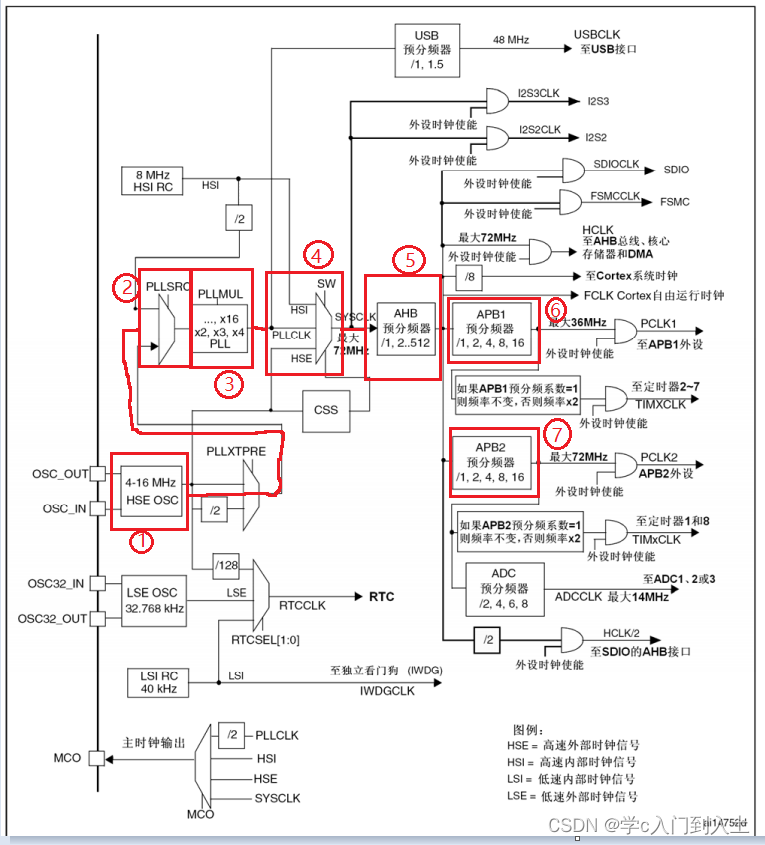

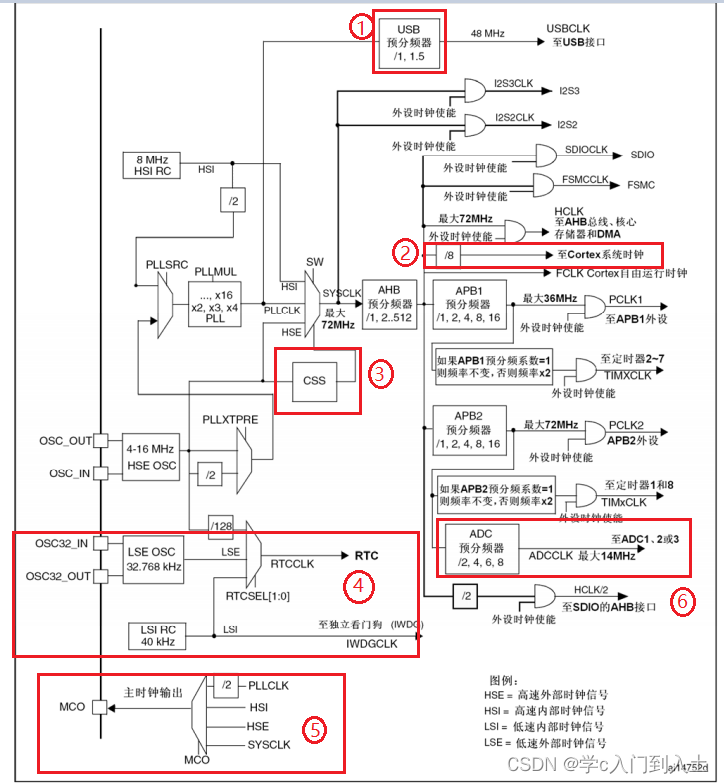

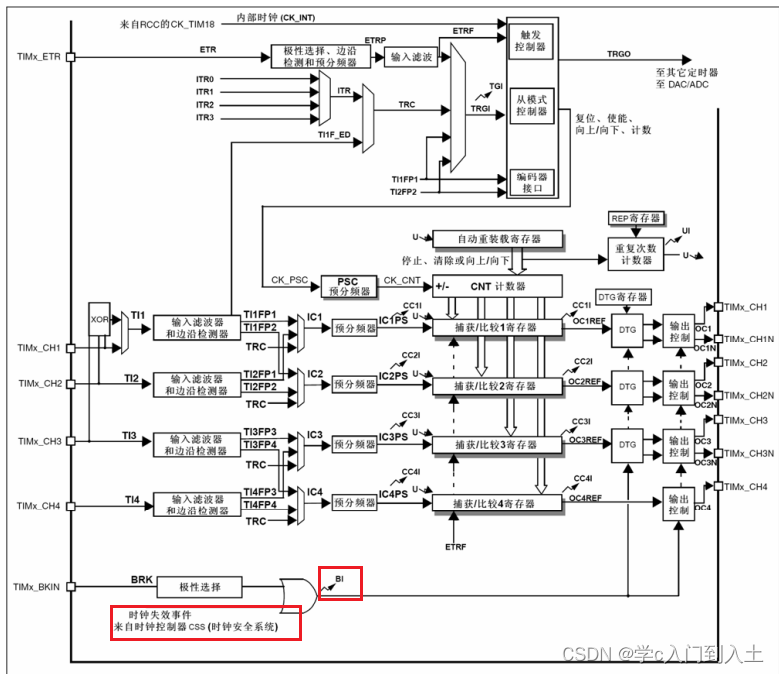

一、时钟树系统时钟

我们打开STM32的手册STM32FXX手册在手册56页找到我们的时钟树框图。

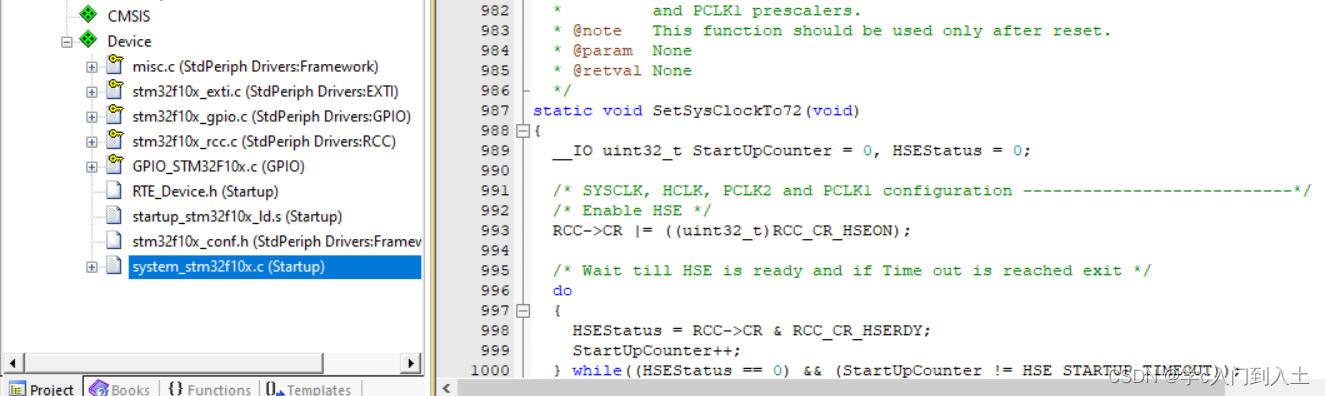

时钟树中这么多东西我们该这么来看呢这里我选取了一条主线是固件库函数中的SetSysClockTo72 ()以这个函数的编写流程来展开旁边的就在这条主线中分支介绍。既然是固件库函数可以看我前面的STM32固件库点亮LED这篇文章。我们在固件库中找到system_stm32f10x.这个文件在其中找到SetSysClockTo72这个函数。

因为其中的注释是英文且其中配置时钟时也加入了别的类型时钟配置我把它整理成我们需要的样子和上面时钟树我画的流程图对应起来代码如下

static void SetSysClockTo72(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

/*1.使能HSE */

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

/* 等待HSE启动稳定并做超时处理 */

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

/*使能Flash预存取缓冲区*/

FLASH->ACR |= FLASH_ACR_PRFTBE;

/*设置系统时钟周期与Flash访问的时间比例统一设置成2*/

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2;

/*2.设置AHB、APB1、APB2的预分频因子*/

/* HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

/* PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

/* PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;

/* 3.设置PLL时钟来源和倍频因子 PLLCLK = HSE * 9 = 72 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

/* 4.使能PLL */

RCC->CR |= RCC_CR_PLLON;

/* 5.等待PLL时钟被配置成功稳定运行 */

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/* 6.选择PLL作为系统时钟的来源 */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/*7.确定系统时钟来源已经被设置成PLLCLK*/

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

}

else

{ /*如果HSE时钟启动失败我们可以在这里添加错误代码*/

}

}1、HSE高速外部时钟信号

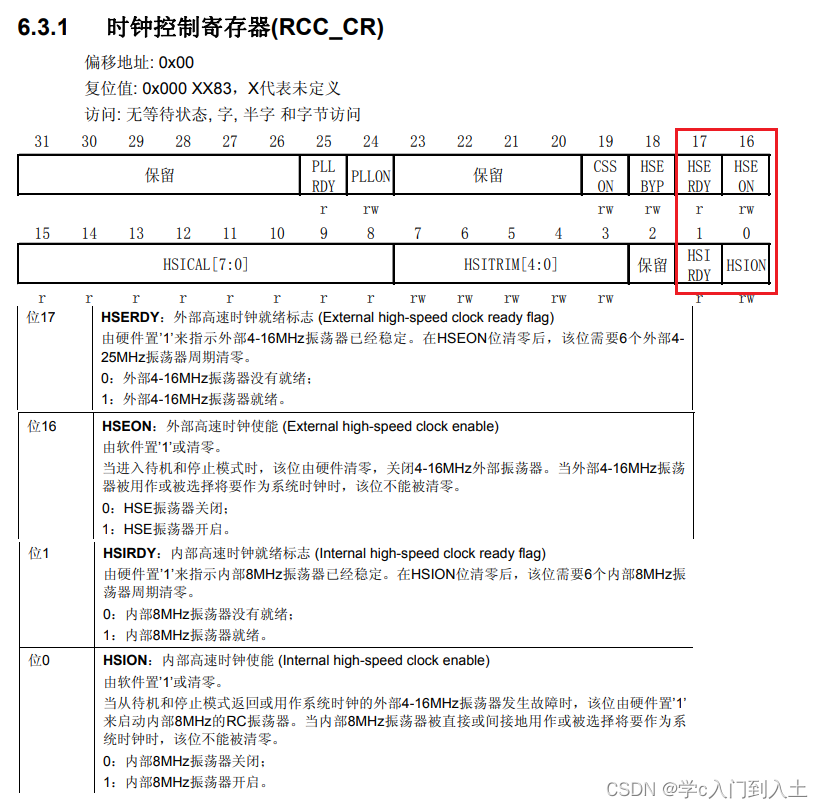

HSE是高速外部时钟信号由我们的外部时钟电路提供可以是有源晶振或者是无源晶振提供频率一般是8MHZ。使用无源晶振时钟从OSC_IN和OSC_OUT引脚进入且必须搭配谐振电容来使用。我们可以操作RCC-CR寄存器的16HSEON位来使能HSE。因为晶振发生频率需要一定时间我们还得读取RCC-CR寄存器的17位HSERDY)时钟是否已经准备就绪。

既然有外部那么就有内部HSI高速内部时钟信号它提供的时钟信号是8MHZ且如果作为PLL时钟来源的话必定被2分频我们可以操作RCC-CR寄存器的0位来使能HSI和读取RCC-CR寄存器的1位HEIRDY时钟是否以经准备就绪。HSE精度高我们一般使用它作为PLL的时钟来源。HSI的精度低且容易受到温度的影响一般只有HSE失效的时候我们才使用它。

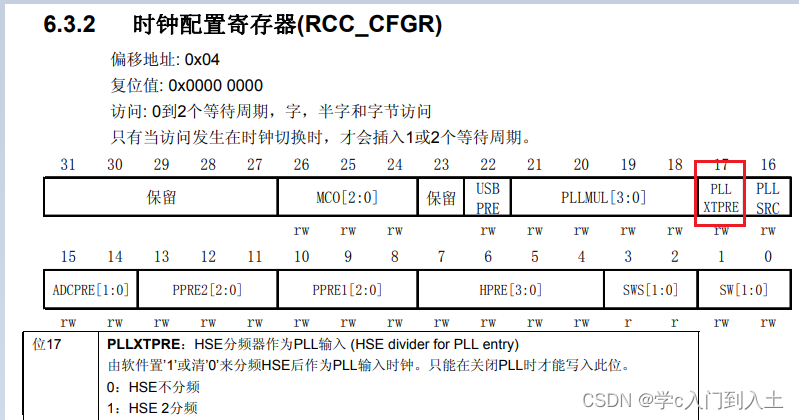

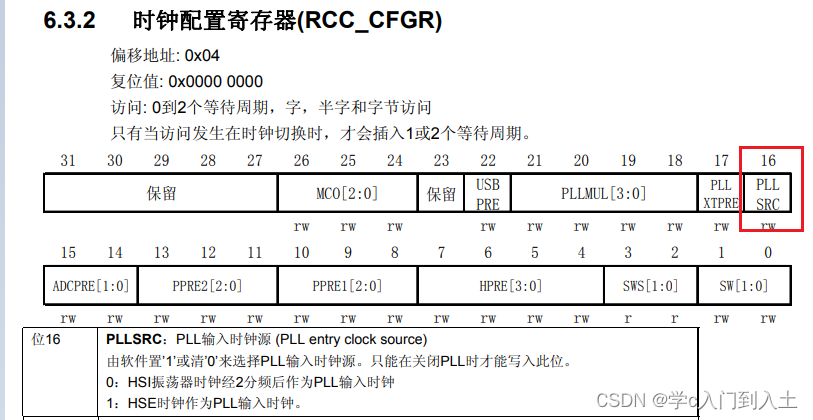

上面我们说了我们一般用HSE做为PLL时钟来源这里这条时钟可以2分频或者不分频由RCC-CFGR寄存器的17位 PLLXTPRE来设置。这里我们一般选择不分频。

2、PLL时钟源

这里可以返回到时钟树看到哪里了建议对着时钟树看本片文章。上面说了PLL时钟的来HSE高速外部时钟信号或者HSI高速内部时钟信号具体用哪个我们可以操作RCC-CFGR寄存器16位PLLSRC。这里我在啰嗦一遍为什么选用HSE高速外部时钟信号因为HSI高速内部时钟信号根据温度和环境的情况频率会飘逸不稳定。

3、PLLCLK锁相环时钟

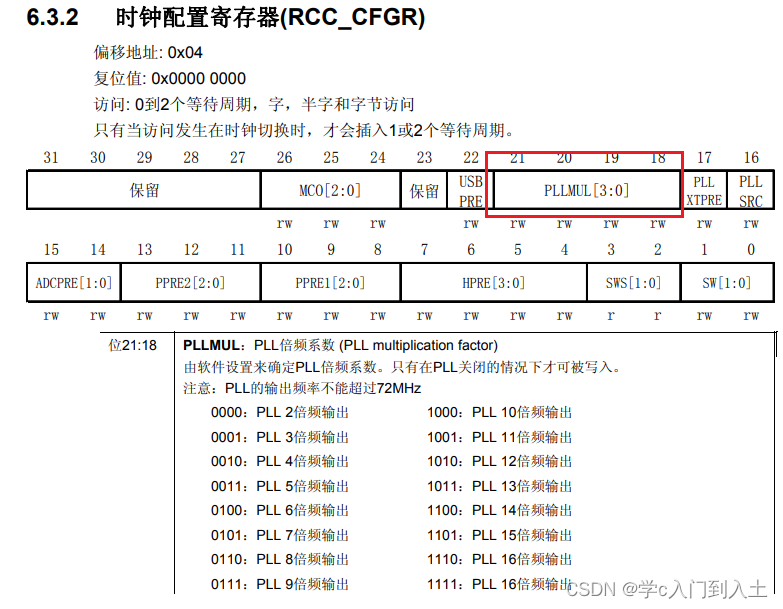

这里可以设置PLL时钟的倍频因子对PLL时钟来源进行倍频可以是2~16倍具体是多少可以通过RCC-CFGR寄存器21~18位PLLMUL[3:0]来配置。ST公司官方推荐72MHZ如果想超频的话自己也可以设置。

4、SYSCLK系统时钟

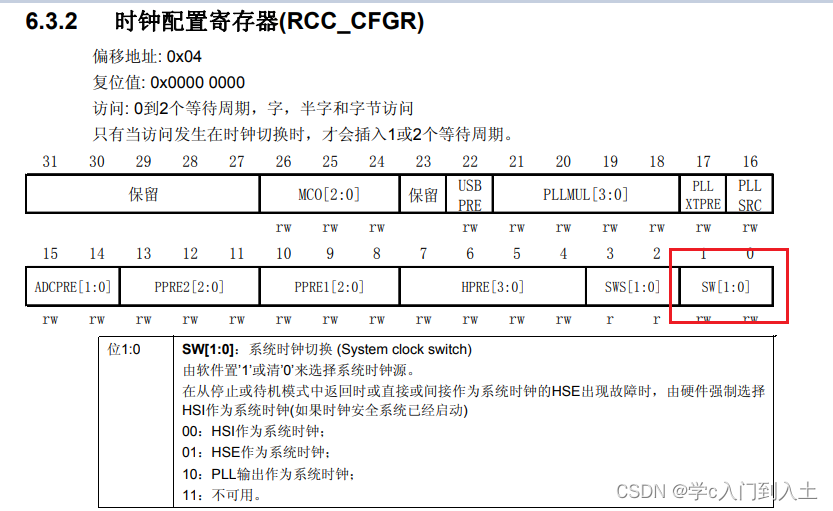

系统时钟的来源我们看时钟树就知道它的来源有三个可以是HSE、HSI、PLLCLK的其中一个具体是那个可以由RCC-CFGR寄存器的0~1SW[1:0]来设置。

5、HCLKAHB总线时钟

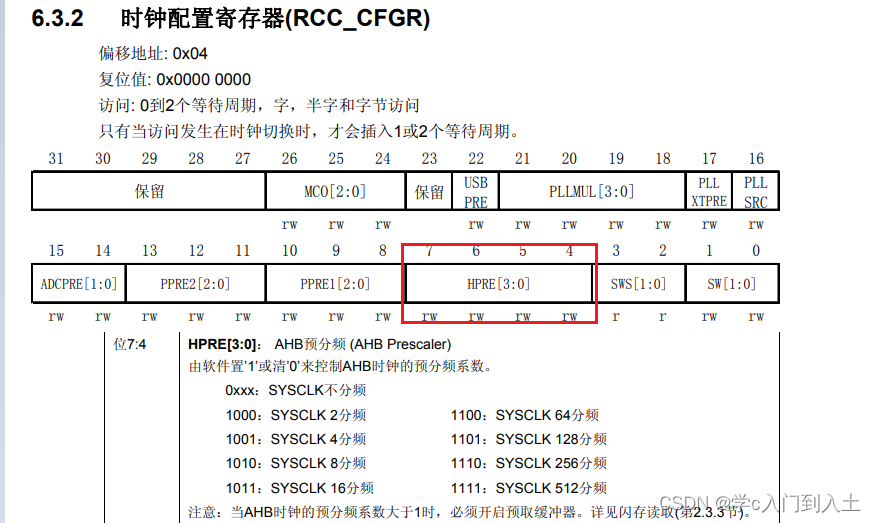

SYSCLK系统时钟通过AHB预分频之后得到的时钟叫HCLKAHB总线时钟分频因子可以是1、2、4、8、16、128、256、512具体由RCC-CFGR寄存器的4~7位HPRE[3:0]来配置。片上外设的时钟都是经过HCLK分频得到的。

HCLKAHB总线时钟出来时大部分片上外设的时钟来源SDIO、FSMC、DMA等外设。

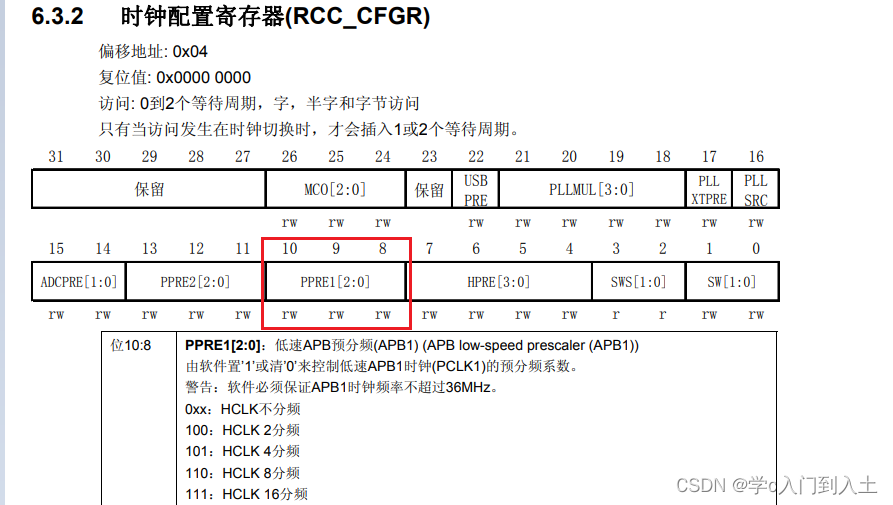

6、HCLK1APB1总线时钟

HCLK1APB1总线时钟由HCLK经过低速APB1预分频得到分频因子可以是1、2、4、8、16具体是由RCC-CFGR寄存器8~10位PPRE[2:0]决定。因为HCLK1属于低速的总线时钟最高为36MHZ片上低速的外设挂载在这条总线上如USART2/3/4/5、SPI2/3、C1/2等。

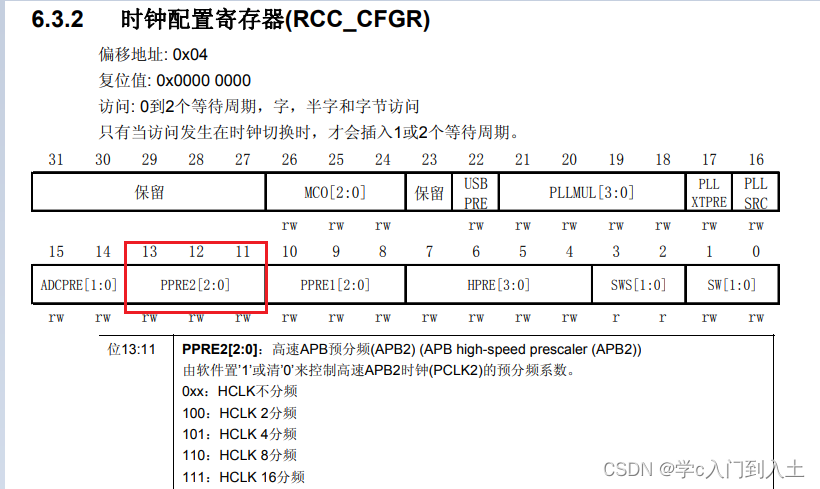

7、HCLK2APB2总线时钟

HCLK2APB2总线时钟由HCLK经过高速APB2预分频得到分频因子可以是1、2、4、8、16具体是由RCC-CFGR寄存器11~13位PPRE2[2:0]决定。因为HCLK2属于高速的总线时钟最高为72MHZ片上高速的外设挂载在这条总线上如USART1、SPI1、GPIO等。

介绍到这里整个系统时钟的介绍就完了对照时钟树也差不多六七成下面对其他时钟做个简单的介绍。

二、时钟树其他时钟

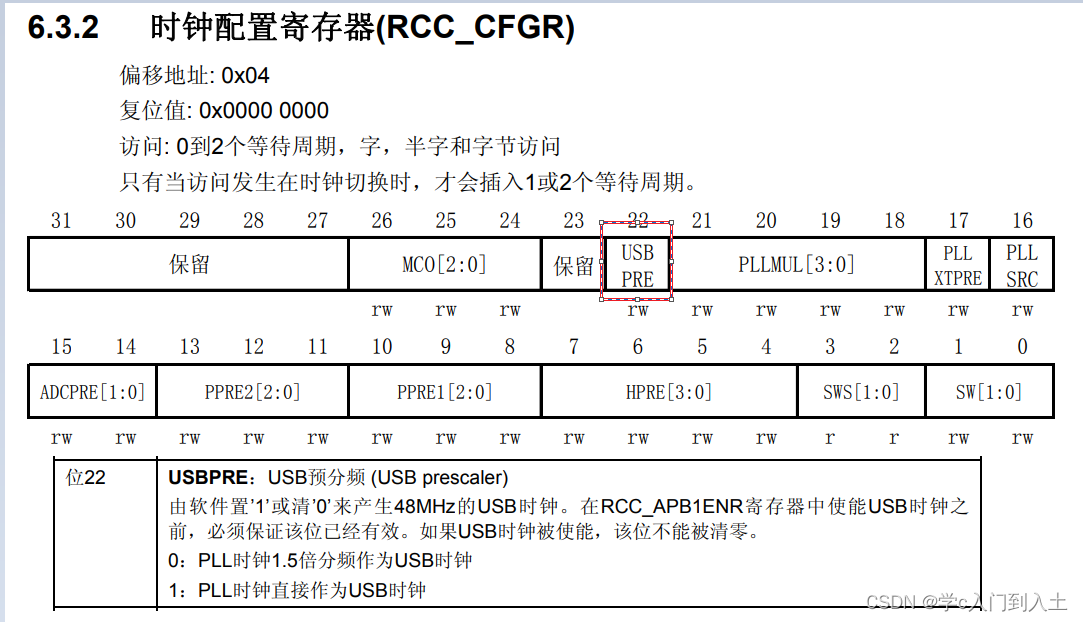

1、USB时钟

USB时钟是由PLLCLK锁相环时钟经过USB预分频器得到的分频因子可以是1、1.5具体可以由RCC-CFGR寄存器22位USBPRE配置。USB时钟对要求较高所以PLLCLK锁相环时钟只能由HSE倍频得到不能使用HSI倍频。

2、Cortex系统时钟

Cortex系统时钟由HCLK8分频得到Cortex系统时钟用来驱动内核的系统定时器SysTick。

3、CSS时钟安全系统

时钟安全系统可以通过软件被激活。一旦其被激活时钟监测器将在HSE启动延迟后被 使能并在HSE时钟关闭后关闭。 如果HSE时钟发生故障HSE时钟被自动关闭时钟失效事件将被送到高级定时器(TIM1和 TIM8)的刹车输入端并产生时钟安全中断CSSI允许软件完成营救操作比如使用HSI。此CSSI中断连接到 Cortex™-M3的NMI中断(不可屏蔽中断)。

注意 一旦CSS被激活并且HSE时钟出现故障CSS中断就产生并且NMI也自动产生。NMI将被不 断执行直到CSS中断挂起位被清除。因此在NMI的处理程序中必须通过设置时钟中断寄存器 (RCC_CIR)里的CSSC位来清除CSS中断。 如果HSE被直接或间接地作为系统时钟(间接的意思是它被作为PLL输入时钟并且 PLL时钟被作为系统时钟)时钟故障将导致系统时钟自动切换到HSI振荡器同时外部HSE时钟将被关闭。在时钟失效时如果HSE时钟(被分频或未被分频)是用作系统时钟的PLL的输 入时钟PLL也将被关闭。

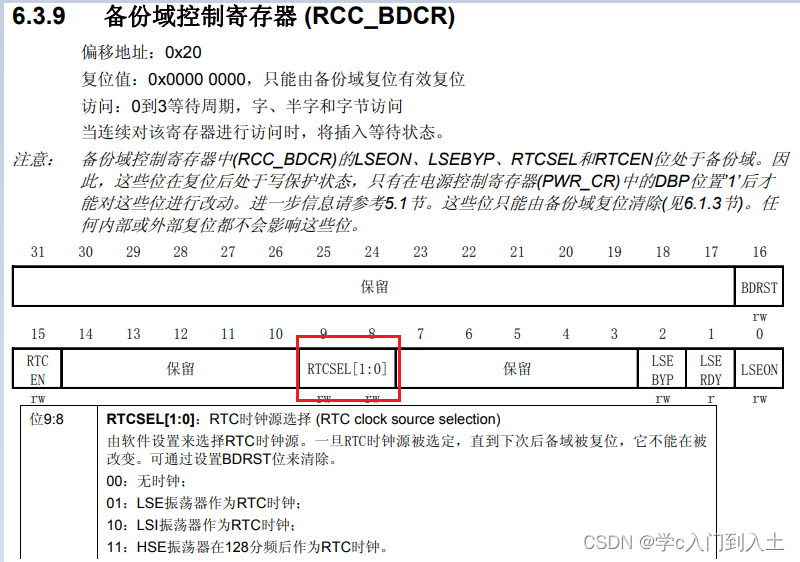

4、RTC时钟、独立看门狗时钟

RTC时钟可以由HSE/128分频或者由LSE低速外部时钟信号得到HSI高速内部时钟信号也行频率为32.768KHZ具体哪个时钟信号由RCC-BDCR寄存器的9~8位RTCSEL[1:0]配置。独立看门狗时钟只能由LSI低速内部时钟信号提供频率为30~60KHZ一般取40KHZ。

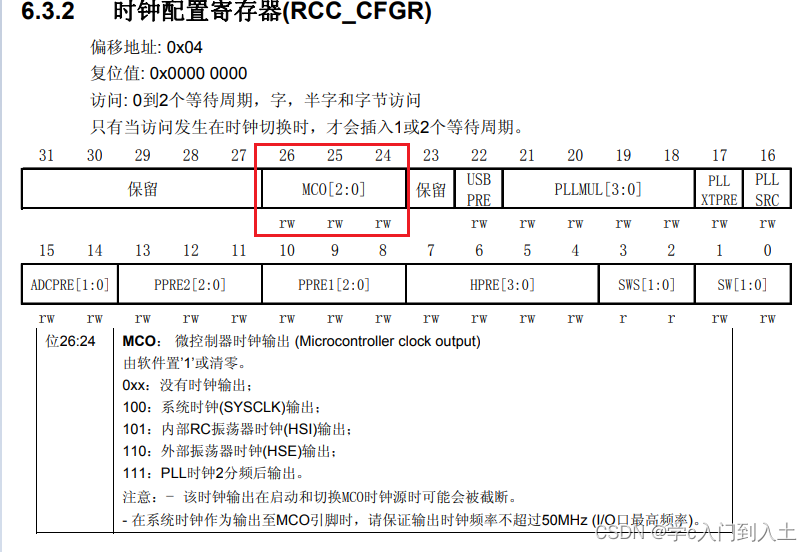

5、MCO时钟

MCO是Microcontroller Clock Output是微控制器时钟输出引脚主要作用是对外提供时钟相当于一个有源晶振时钟来源可以是PLLCLK/2锁相环时钟2分频、HSI高速内部时钟信号HSE高速外部时钟信号、SYSCLK系统时钟具体是哪个可以由RCC-CFGR寄存器26~24MOC[2:0]来配置。除了对外部提供时钟信号外我们还可以通过示波器监控MCO引脚的时钟输出来验证系统时钟配置是否正确。

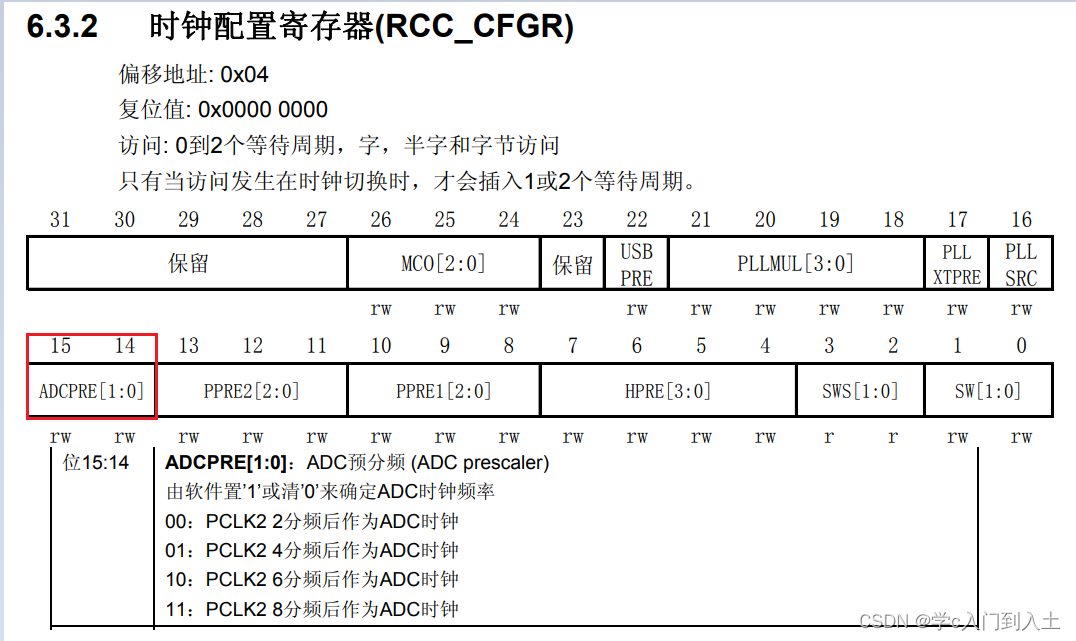

6、ADC时钟

ADC时钟由PCLK2APB2总线时钟经过ADC预分频得到分频因子可以是2、4、6、8具体由RCC-CFGR寄存器的15~14位ADCPRE[1:0]来配置。ADC时钟很奇怪最高14MHZ我们逆推一下PCLK2的时钟只能是28MHZ、56MHZ、84MHZ、112MHZ。鉴于PCLK2时钟最高只有72MHZ所以我们只能取28MHZ、56MHZ。

到这我们的时钟树已经全部介绍完毕关注我后面我会更新STM32的所有特色外设