FPGA纯verilog代码实现图像缩放,两种插值算法任意尺寸缩放,提供3套工程源码_verilog 图像放大

| 阿里云国内75折 回扣 微信号:monov8 |

| 阿里云国际,腾讯云国际,低至75折。AWS 93折 免费开户实名账号 代冲值 优惠多多 微信号:monov8 飞机:@monov6 |

目录

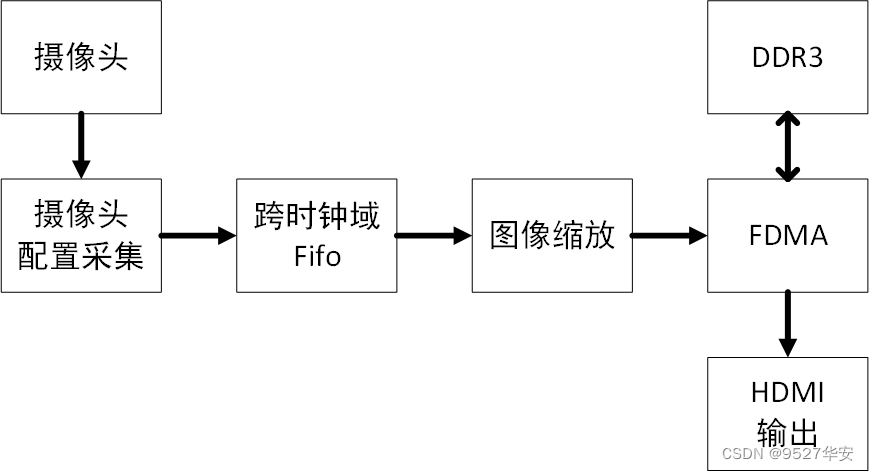

1、设计思路和架构

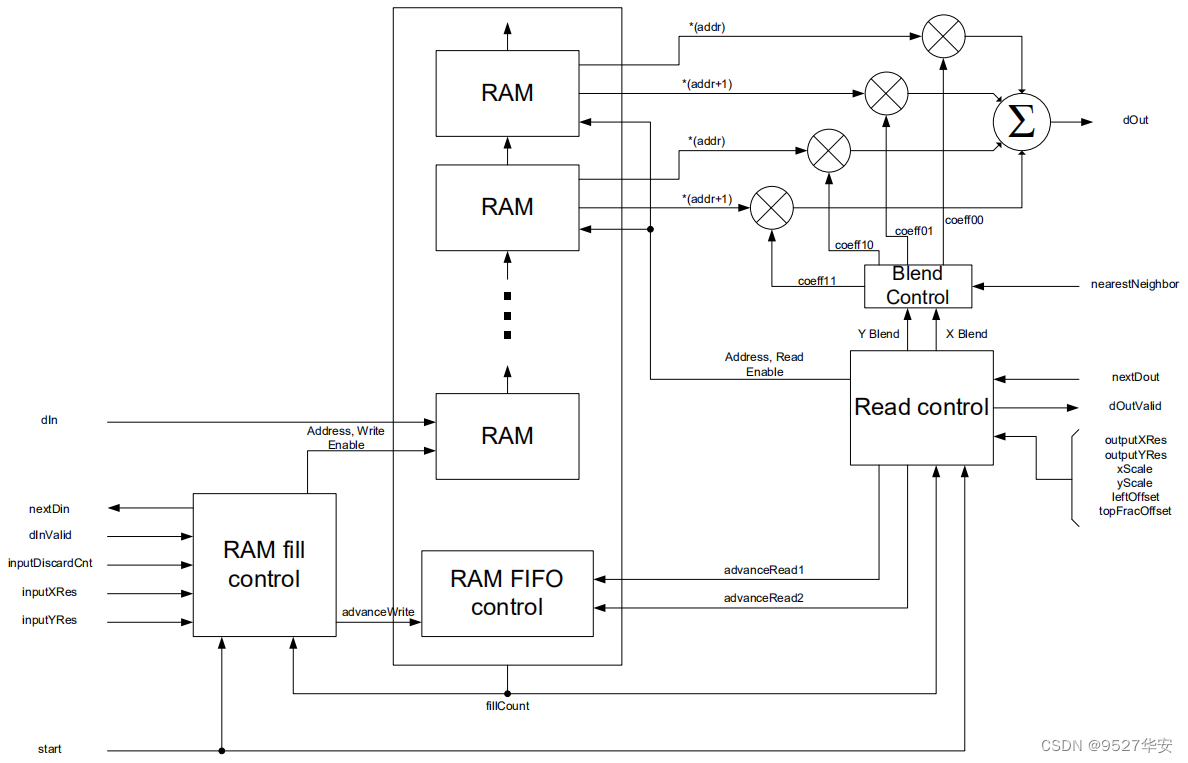

本设计将常用的双线性插值和邻域插值算法融合为一个代码中通过输入参数选择某一种算法代码使用纯verilog实现没有任何ip可在Xilinx、Intel、国产FPGA间任意移植代码以ram和fifo为核心进行数据缓存和插值实现设计架构如下

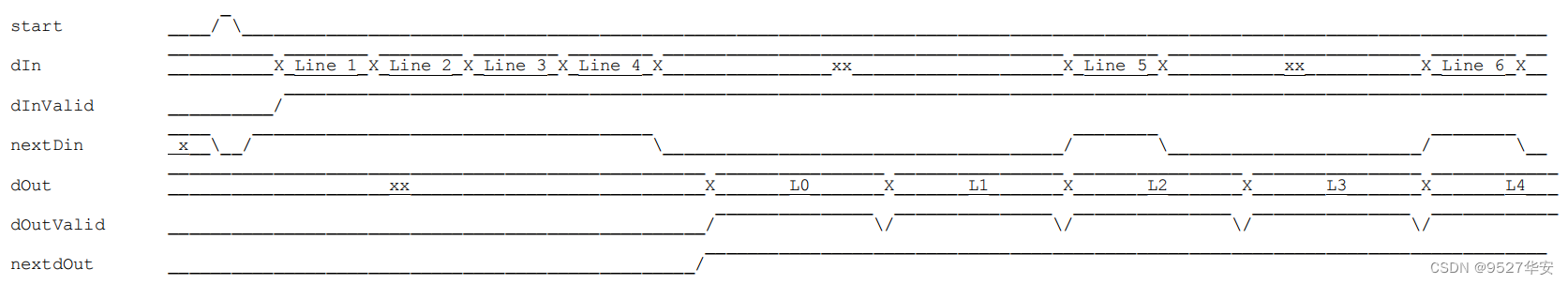

视频输入时序要求如下

输入像素数据在dInValid和nextDin同时为高时方可改变

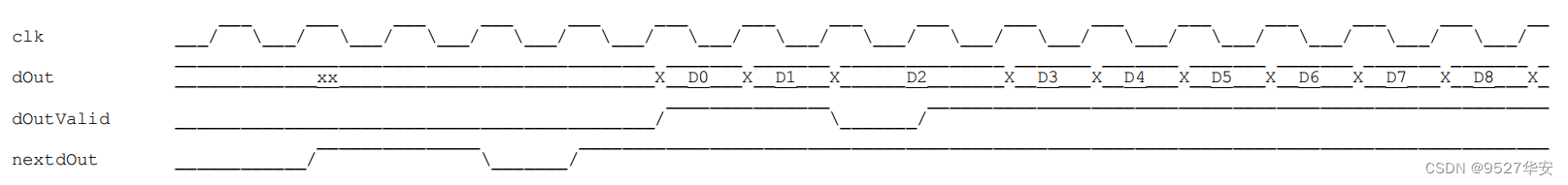

视频输出时序要求如下

输出像素数据在dOutValid 和nextdOut同时为高时才能输出

2、纯verilog代码搭建不带任何ip

代码使用纯verilog实现没有任何ip可在Xilinx、Intel、国产FPGA间任意移植

图像缩放的实现方式很多最简单的莫过于Xilinx的HLS方式实现用opencv的库以c++语言几行代码即可完成关于HLS实现图像缩放请参考我之前写的文章HLS实现图像缩放

网上也有其他图像缩放例程代码但大多使用了IP导致在其他FPGA器件上移植变得困难通用性不好

相比之下本设计代码就具有通用性

代码架构如图

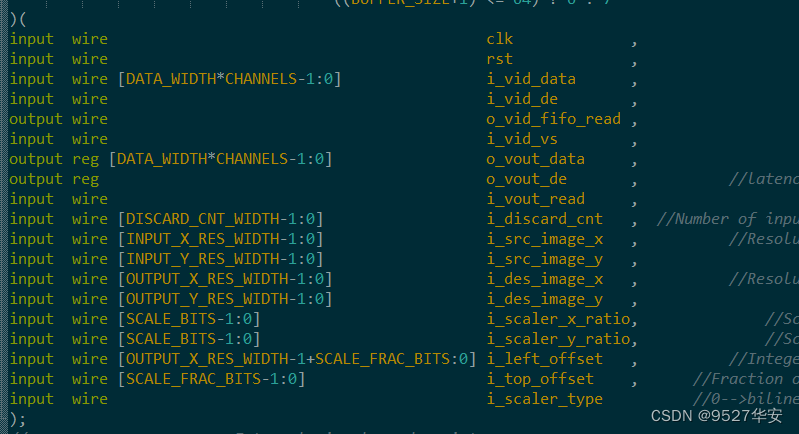

其中顶层接口部分如下

3、双线性插值和邻域插值算法

本设计将常用的双线性插值和邻域插值算法融合为一个代码中通过输入参数选择某一种算法

具体选择参数如下

input wire i_scaler_type //0-->bilinear;1-->neighbor

通过输入i_scaler_type 的值即可选择

输入0选择双线性插值算法

输入1选择邻域插值算法

关于这两种算法的数学差异请参考我之前写的文章HLS实现图像缩放

4、vivado和matlab联合仿真及结果

第一步网上下载一张1280X720的图片并用matlab将图片转换为RGB格式的txt文档

第二步在vivado下设计tstbench将RGB格式的txt文档作为视频输入源给到图像缩放模块并将缩放后的图像数据写入输出txt文档

第二步用matlab将输出txt文档转换为图片并于原图一并输出显示以做比较

根据以上方法得到以下仿真结果

双线性插值算法原图1280X720缩小到800x600如下

邻域插值算法原图1280X720缩小到800x600如下

双线性插值算法原图1280X720放大到1920x1080如下

邻域插值算法原图1280X720放大到1920x1080如下

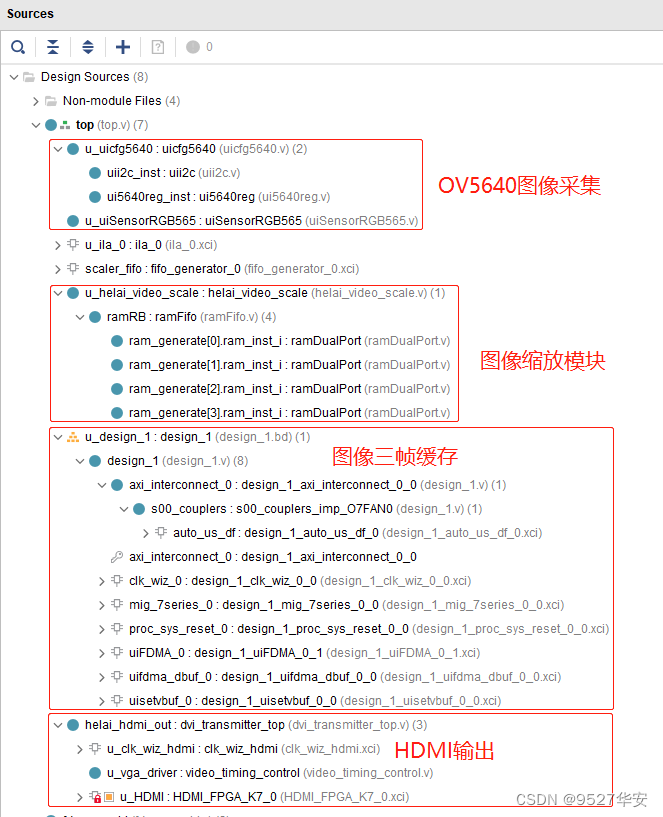

5、工程代码1720P原始摄像头采集显示

三套工程的设计架构都一样如下

开发板Xilinx Kintex7开发板

开发环境Vivado2019.1

输入OV5640摄像头分辨率1280x720p

输出HDMI1080P分辨率下的720P有效区域显示

工程作用采集原始的720P图像以便和后面的缩小效果作比较

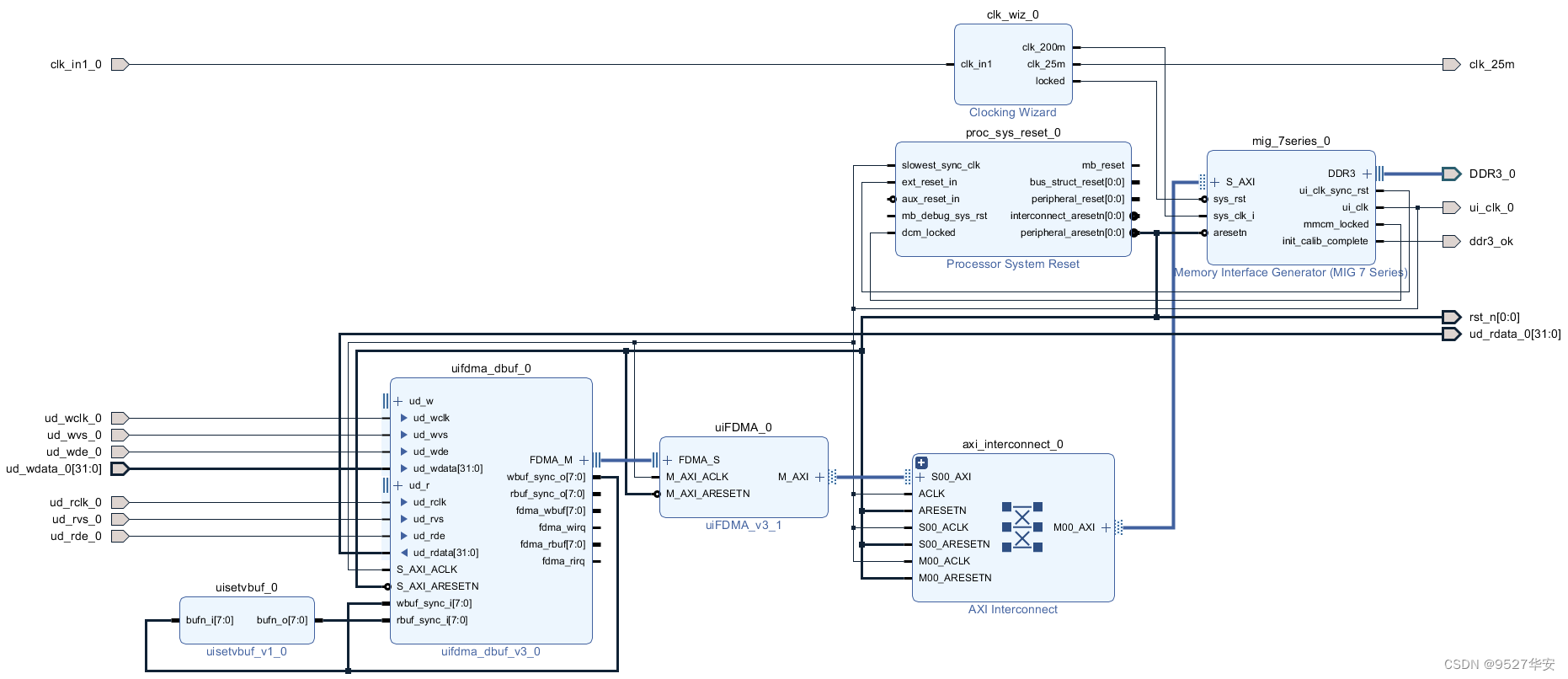

工程BD如下

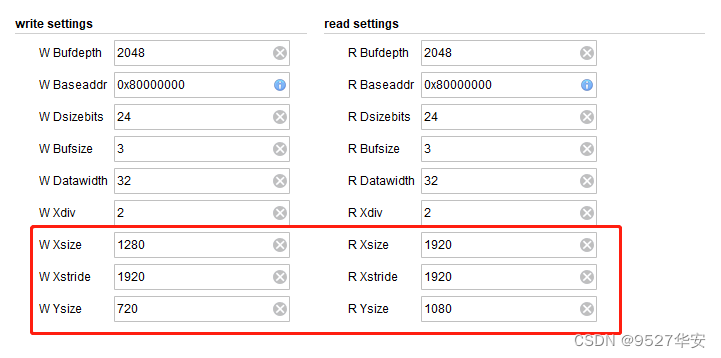

其中FDMA控制器配置如下

FDMA架构实现了视频到DDR3的三帧缓存读写关于FDMA请参考我之前写的文章FDMA视频到DDR3的三帧缓存

工程代码架构如下

工程的资源消耗和功耗如下

6、工程代码2720P缩小到800x600P显示

开发板Xilinx Kintex7开发板

开发环境Vivado2019.1

输入OV5640摄像头分辨率1280x720p

输出HDMI1080P分辨率下的800x600有效区域显示

工程作用1280x720原图缩小到800x600并和原图作比较

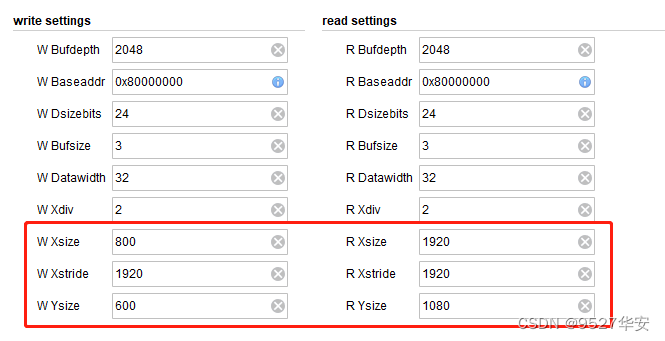

工程设计框架、BD、工程代码架构和工程1一样FDMA配置如下

7、工程代码3720P缩放大1920x1080P显示

开发板Xilinx Kintex7开发板

开发环境Vivado2019.1

输入OV5640摄像头分辨率1280x720p

输出HDMI1080P分辨率下的800x600有效区域显示

工程作用1280x720原图放大到1920x1080并和原图作比较

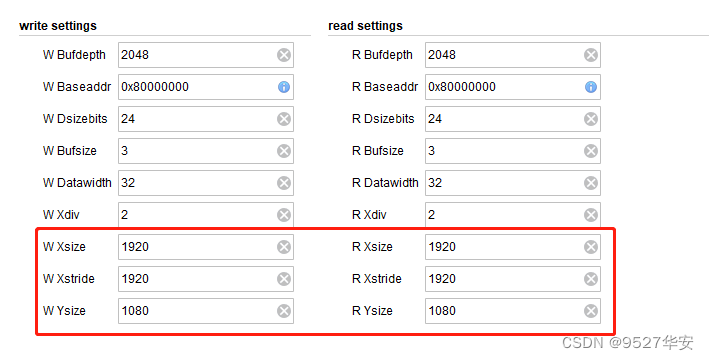

工程设计框架、BD、工程代码架构和工程1一样FDMA配置如下

8、上板调试验证并演示

板子连接如下

工程1原图1280x720输出效果如下

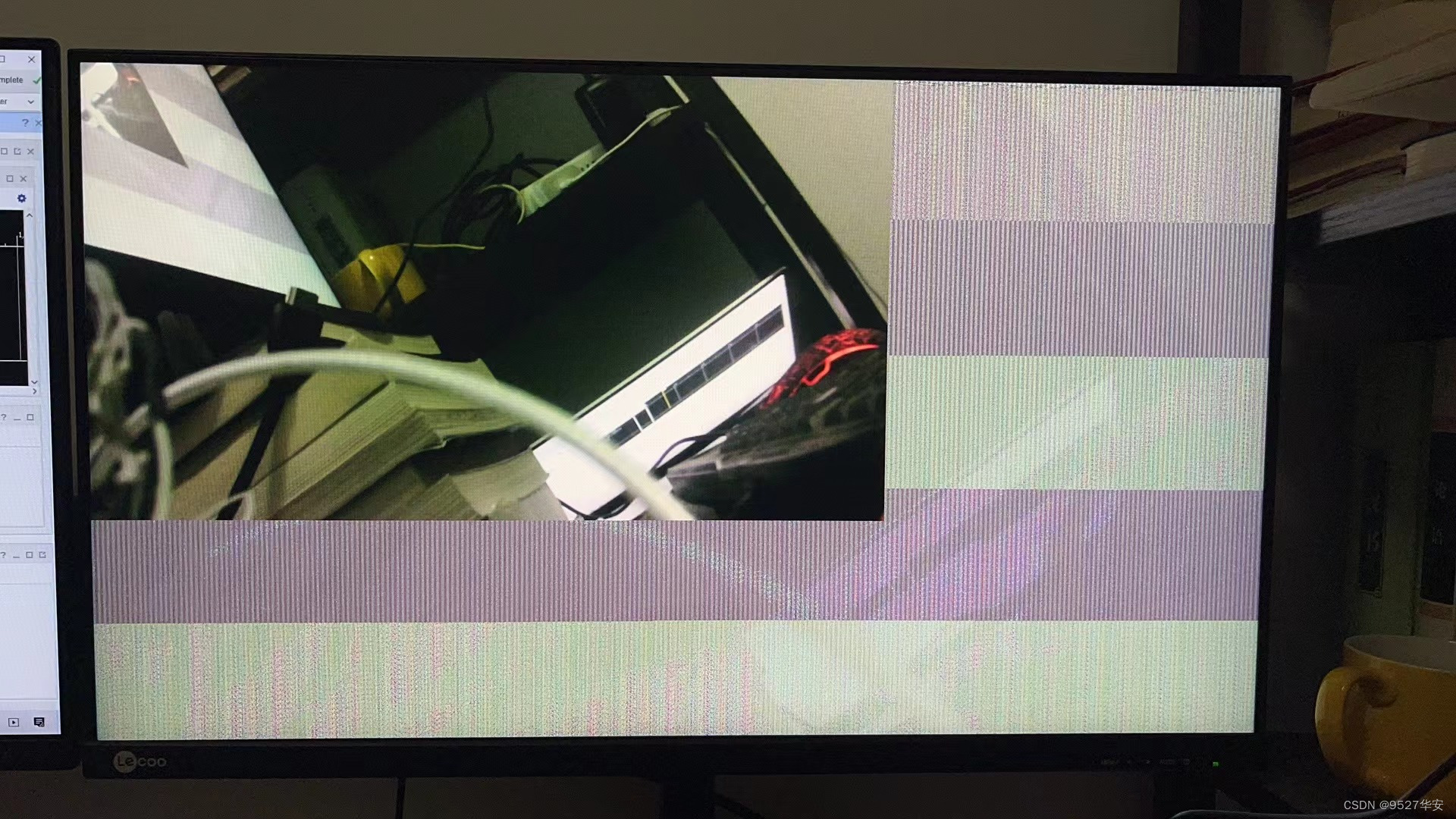

工程2原图1280x720缩小到800x600输出效果如下

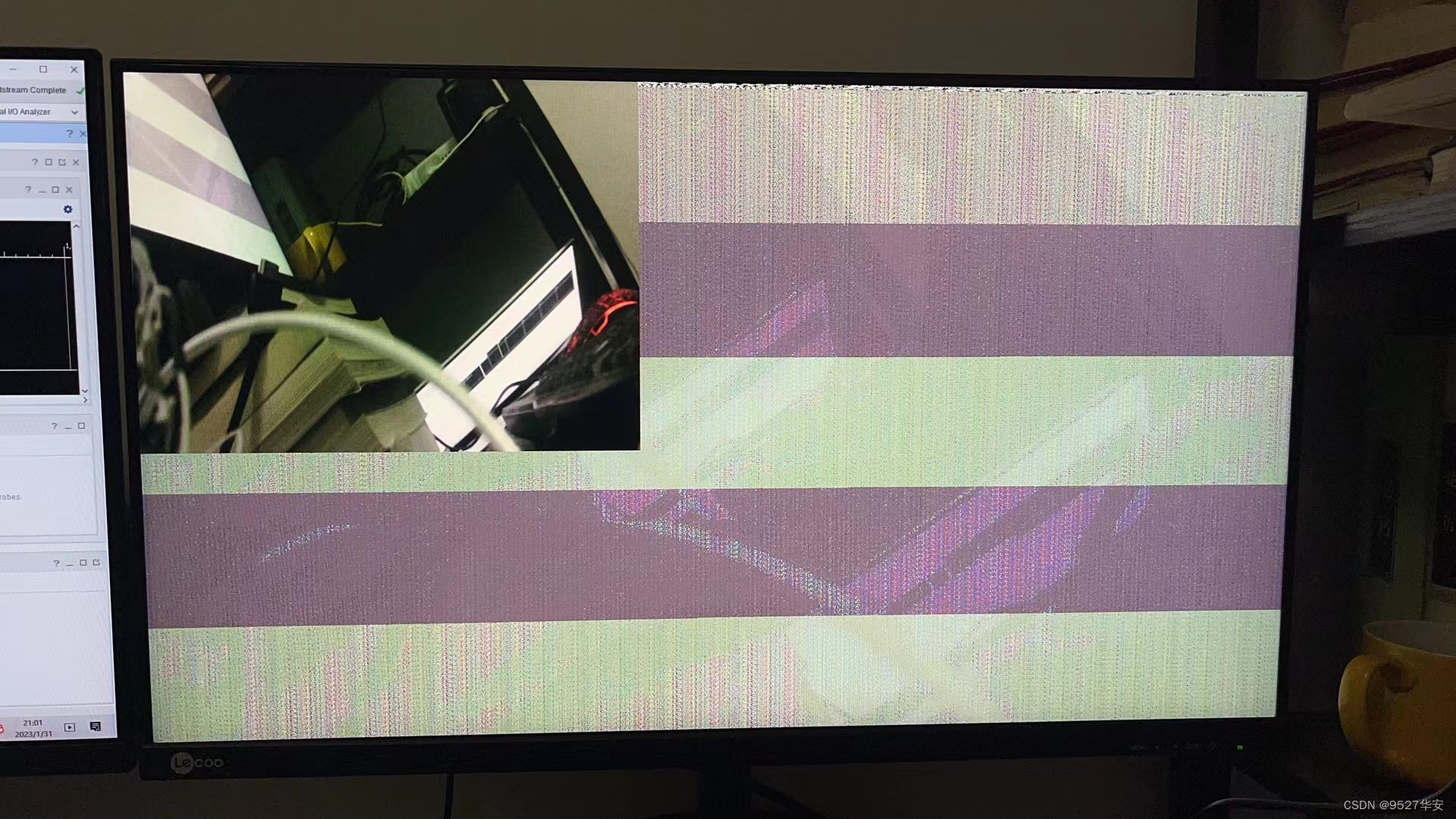

工程3原图1280x720放大到1920x1080输出效果如下

动态视频演示如下

FPGA纯verilog代码实现图像缩放

9、福利工程源码获取

福利工程代码的获取

代码太大无法邮箱发送以某度网盘链接方式发送

资料如下获取方式私。

网盘资料如下