Verilog HDL行为级建模

| 阿里云国内75折 回扣 微信号:monov8 |

| 阿里云国际,腾讯云国际,低至75折。AWS 93折 免费开户实名账号 代冲值 优惠多多 微信号:monov8 飞机:@monov6 |

⭐本专栏针对FPGA进行入门学习从数电中常见的逻辑代数讲起结合Verilog HDL语言学习与仿真主要对组合逻辑电路与时序逻辑电路进行分析与设计对状态机FSM进行剖析与建模。

🔥文章和代码已归档至【Github仓库hardware-tutorial】需要的朋友们自取。或者公众号【AIShareLab】回复 FPGA 也可获取。

文章目录

行为级建模就是描述数字逻辑电路的功能和算法。

在Verilog中行为级描述主要使用由关键词initial或always定义的两种结构类型的语句。一个模块的内部可以包含多个initial或always语句。

initial语句是一条初始化语句仅执行一次经常用于测试模块中对激励信号进行描述在硬件电路的行为描述中有时为了仿真的需要也用initial语句给寄存器变量赋初值。

initial语句主要是一条面向仿真的过程语句不能用于逻辑综合 。这里不介绍它的用法。

在always结构型语句内部有一系列过程性赋值语句用来描述电路的功能行为。

行为级建模基础

下面介绍行为级建模中经常使用的语句

- always语句结构及过程赋值语句

- 条件语句if-else

- 多路分支语句case-endcase

- for循环语句例如 for等

1. always语句的一般用法

always @(事件控制表达式)

begin块名

块内局部变量的定义;

过程赋值语句包括高级语句;

end

“@”称为事件控制运算符用于挂起某个动作直到事件发生。“事件控制表达式”也称为敏感事件表它是后面begin和end之间的语句执行的条件。当事件发生或某一特定的条件变为“真”时后面的过程赋值语句就会被执行。

begin…end 之间只有一条语句时关键词可以省略

begin…end 之间的多条语句被称为顺序语句块。可以给语句块取一个名字称为有名块。

2. 条件语句 if语句

条件语句就是根据判断条件是否成立确定下一步的运算。

Verilog语言中有3种形式的if语句

1 if (condition_expr) true_statement;

2 if (condition_expr) true_statement;

else false_ statement;

3 if (condition_expr1) true_statement1;

else if (condition_expr2) true_statement2;

else if (condition_expr3) true_statement3;

……

else default_statement;

if后面的条件表达式一般为逻辑表达式或关系表达式。执行if语句时首先计算表达式的值若结果为0、x或z按“假”处理若结果为1按“真”处理并执行相应的语句。

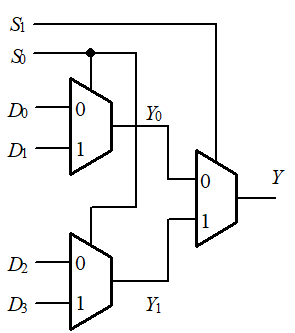

例使用if-else语句对4选1数据选择器的行为进行描述

module mux4to1_bh(D, S, Y);

input [3:0] D; //输入端口

input [1:0] S; //输入端口

output reg Y; //输出端口及变量数据类型

always @(D, S) //电路功能描述,或@(D or S)

if (S == 2’b00) Y = D[0];

else if (S== 2’b01) Y = D[1];

else if (S== 2’b10) Y = D[2];

else Y = D[3];

endmodule

注意过程赋值语句只能给寄存器型变量赋值因此输出变量Y的数据类型定义为reg。

3. 多路分支语句case语句

是一种多分支条件选择语句一般形式如下

case (case_expr)

item_expr1: statement1;

item_expr2: statement2;

……

default: default_statement; //default语句可以省略

endcase

注意当分支项中的语句是多条语句必须在最前面写上关键词begin在最后写上关键词end成为顺序语句块。

另外用关键词casex和casez表示含有无关项x和高阻z的情况。

例对具有使能端En 的4选1数据选择器的行为进行Verilog描述。当En=0时数据选择器工作En=1时禁止工作输出为0。

module mux4to1_bh (D, S, En,Y);

input [3:0] D[1:0] S input En;

output reg Y

always @(D, S, En) //2001, 2005 syntax或@(D or S or En)

begin

if (En==1) Y = 0; //En=1时输出为0

else //En=0时选择器工作

case (S)

2’d0: Y = D[0];

2’d1: Y = D[1];

2’d2: Y = D[2];

2’d3: Y = D[3];

endcase

end

endmodule

4. for循环语句

一般形式如下

for (initial_assignment; condition; step_assignment)

statement

initial_assignment 为循环变量的初始值。

condition为循环的条件若为真执行过程赋值语句statement若不成立循环结束执行for后面的语句。

step_assignment为循环变量的步长每次迭代后循环变量将增加或减少一个步长。

试用Verilog语言描述具有高电平使能的3线-8线译码器.

module decoder3to8_bh(A,En,Y);

input [2:0] AEn;

output reg [7:0] Y;

integer k; //声明一个整型变量k

always @(A, En) // 2001, 2005 syntax

begin

Y = 8’b1111_1111; //设译码器输出的默认值

for(k = 0; k <= 7; k = k+1) //下面的if-else语句循环8次

if ((En==1) && (A== k) )

Y[k] = 0; //当En=1时根据A进行译码

else

Y[k] = 1; //处理使能无效或输入无效的情况

end

endmodule