基于linux5.15.5的IMX 参考手册 --- 4

| 阿里云国内75折 回扣 微信号:monov8 |

| 阿里云国际,腾讯云国际,低至75折。AWS 93折 免费开户实名账号 代冲值 优惠多多 微信号:monov8 飞机:@monov6 |

基于linux5.15.5的IMX 参考手册 — 4

第三章 存储

3.1 AHB-to-APBH Bridge with DMA (APBH-Bridge-DMA)

3.1.1概述

AHB-to-APBH桥接为处理器提供了运行在AHB的HCLK上的廉价外围连接总线。APBH中的H表示APBH与HCLK同步。

AHB-to-APBH桥接器包括AHB-to-APB的PIO桥接器用于内存映射I/O到APB设备以及用于该总线上设备的中央DMA设备和用于Arm核心的矢量中断控制器。每一个APB外设包括矢量中断控制器在本文档的其他地方各自的章节中都有记录。

这些设备没有单独的DMA总线。DMA使用APBH总线和AHB-to-APB桥接功能使用APBH之间的争用是由内部仲裁逻辑来调解的。对于这两个单元之间的争用DMA优先AHB从站将通过它的HREADY输出报告“没有准备好”直到桥接传输完成。仲裁者跟踪反复的锁定并反转优先级确保Arm平台每四次在APB上传输一次。

3.1.1.1硬件操作

SDMA控制器负责在MCU存储空间和外设之间传输数据具有以下特点。

•多通道DMA支持多达32个时分多路DMA通道

•采用16位指令集微型risc引擎

•每个通道执行一个特定的脚本

•具有基于两级优先级的抢占式多任务处理的快速上下文切换

•4kbytes ROM包含启动脚本(即启动代码)和其他常见的实用程序可以被ram定位的脚本引用

•8kbyte RAM区域被划分为处理器上下文区域和用于存储从系统内存下载的通道脚本的代码空间区域。

3.1.1.2软件操作

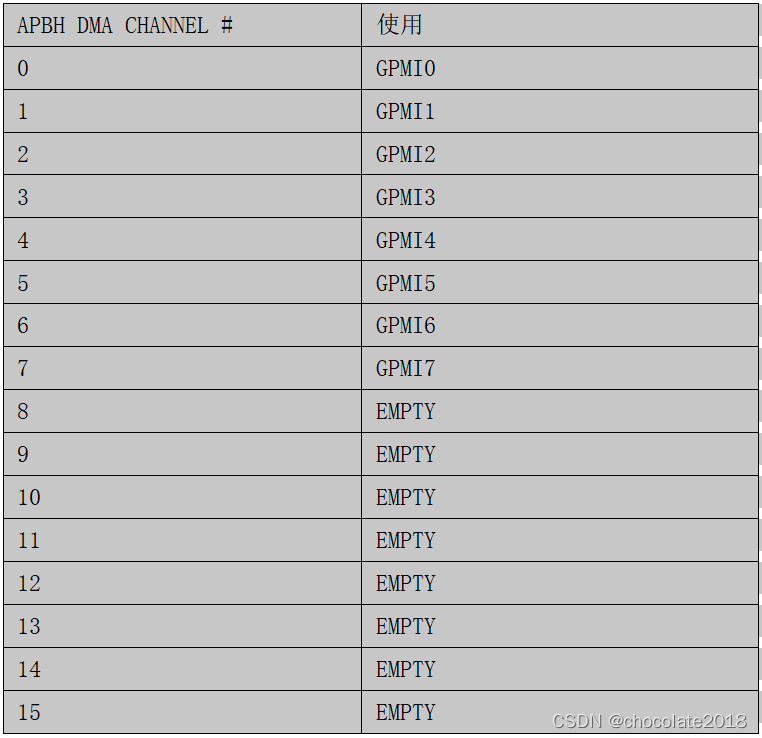

DMA支持16个通道的DMA服务如下表所示。共享的DMA资源允许每个独立通道遵循一个简单的链接命令列表。命令链使用通用结构建立。

表24. APBH DMA信道分配

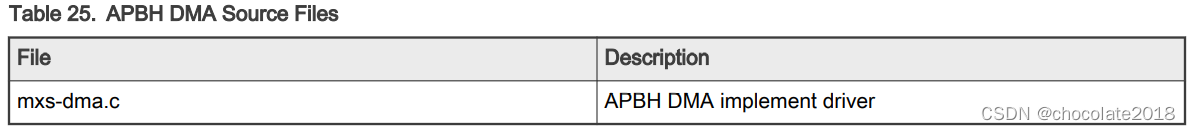

3.1.1.3源代码结构

下表显示了drivers/dma/中可用的源文件

3.1.1.4菜单配置选项

在菜单配置中启用以下模块:

• Device Drivers > DMA Engine support > MXS DMA support.

3.1.1.5编程接口

该模块实现了标准的DMA API。请参阅位于Linux文档包中的API文档了解驱动程序(如GPMI NAND驱动程序)中实现的函数的更多信息。

3.2 EIM NOR

3.2.1介绍

EIM (External Interface Module) NOR驱动支持并行NOR flash。

3.2.2硬件操作

默认情况下i.MX 6Quad/6Dual SABRE-AI板上有一个并行NOR。并行NOR比SPI NOR有更多的引脚。

在一些单板上配备了M29W256GL7AN6E。有关并行NOR的详细信息请参阅数据表。

3.2.3软件操作

与SPI NOR类似并行NOR使用MTD子系统。因为并行NOR非常小所以您可以只使用jffs2而不能为它使用UBIFS。

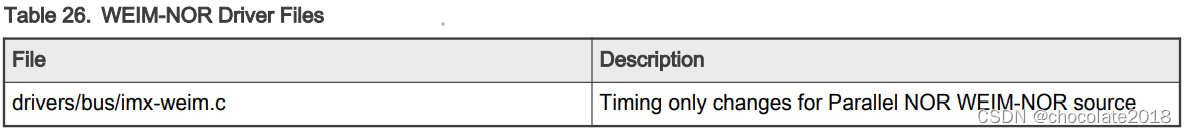

3.2.4源代码

3.2.5使能EIM NOR

请参考DTS文件来启用EIM NOR: mx6q-sabreauto-gpmi-weim.dts 或 imx6dl-sabreauto-gpmi-weim.dts。

3.3 MMC / SD / SDIO主机

3.3.1介绍

MultiMediaCard (MMC)/ Secure Digital (SD)/ Secure Digital Input Output (SDIO)主机驱动实现了一个标准的Linux驱动接口到ultra MMC/SD主机控制器(uSDHC)。

主机驱动程序是Linux内核MMC框架的一部分。

MMC驱动具有以下特性:

•SD3.0和SDIO 2.0卡的1位或4位操作到目前为止我们支持SDIO v2.0AR6003已验证。

•支持插拔卡检测。

•支持标准MMC命令。

•PIO和DMA数据传输。

•支持电源管理。

•支持1/4 8位MMC卡操作。

•对于i.MX 6, USDHC支持eMMC4.4 SDR和DDR模式。

•对于i.MX 7Dual, USDHC支持eMMC5.0其中包括HS400和HS200。

•支持SD3.0 SDR50和SDR104模式。

3.3.2硬件操作

MMC通信基于一种先进的11脚串行总线设计用于在低电压范围内工作。uSDHC模块支持MMC同时支持SD内存和I/O功能。uSDHC控制MMC、SD内存和I/O卡向卡发送命令并对卡进行数据存取。SD存储卡系统定义了两种可选通信协议:SD和SPI。uSDHC只支持SD总线协议。

uSDHC命令传输类型和uSDHC命令参数寄存器允许向卡发出命令。uSDHC命令寄存器、系统控制寄存器和协议控制寄存器允许用户指定数据和响应的格式并控制读等待周期。

有四个32位寄存器用于存储来自uSDHC卡的响应。uSDHC读取这四个寄存器以直接获得命令响应。uSDHC使用完全可配置的128x32位FIFO进行读写。缓冲区用作在主机系统和卡之间传输的数据的临时存储反之亦然。uSDHC数据缓冲区存取寄存器位在读或写传输时保存32位数据。

接收数据的步骤如下:

- 当缓冲区接收到的字数超过RD_WML寄存器中设置的字数时uSDHC控制器生成一个DMA请求

- 当接收到这个请求时DMA引擎开始通过读取数据缓冲区访问寄存器将数据从uSDHC FIFO传输到系统内存。

传输数据的步骤如下: - 每当缓冲区空间的数量超过WR_WML寄存器中设置的值时uSDHC控制器就会生成一个DMA请求。

- 在接收到这请求后DMA引擎开始将数据从系统内存移动到uSDHC FIFO方法是写入数据缓冲区访问寄存器获取一些预定义的字节。

只读的uSDHC 当前状态和中断状态寄存器提供uSDHC的操作状态、应用FIFO状态、错误条件和中断状态。

当某些事件发生时模块有能力生成中断以及设置相应的状态寄存器位。

uSDHC中断状态使能寄存器和信号使能寄存器允许用户控制这些中断是否发生。

3.3.3软件操作

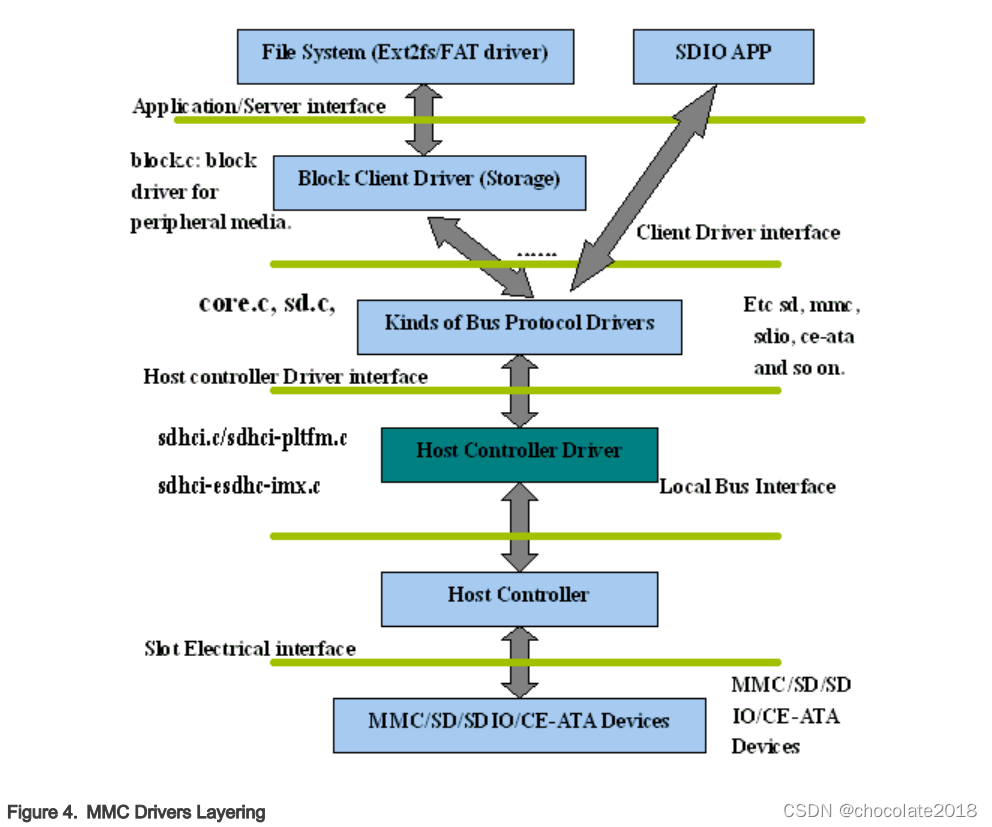

Linux操作系统中包含一个MMC总线驱动程序该驱动程序实现MMC总线协议。MMC块驱动程序处理文件系统读/写调用并使用低级MMC主机控制器接口驱动程序将命令发送给uSDHC。

MMC驱动程序负责实现init、exit、request和set_ios的标准入口点。驱动程序实现以下功能:

uSDHC:

初始化函数esdhc_pltfm_init()初始化平台硬件并将平台相关的标志或值设置为sdhci_host结构。

•退出函数esdhc_pltfm_exit()反初始化平台硬件并释放已分配的内存。

•函数esdhc_pltfm_get_max_clock()获取平台支持的最大SD总线时钟频率。

•函数esdhc_pltfm_get_min_clock()获取平台支持的最小SD总线时钟频率。

•esdhc_pltfm_get_ro()获取卡的只读状态。

•esdhc_execute_tuning()处理调优的准备工作。仅用于SD3.0 UHS-I模式。

•esdhc_set_clock()处理时钟更改请求。

下图显示了与mmc相关的驱动程序是如何分层的。

3.3.4驱动特性

MMC驱动支持以下特性:

•支持多个uSDHC模块。

•提供与Linux MMC核心驱动程序接口的所有入口点。

•MMC和SD卡。

•SDIO卡。

•SD3.0卡片。

•识别数据传输错误如命令超时和CRC错误。

•电源管理。

•它支持被构建为可加载或内置模块

3.3.5源代码结构

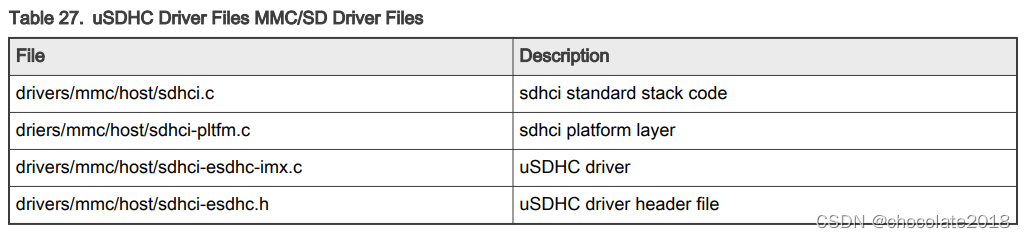

下表显示了drivers/mmc/host中可用的uSDHC源文件。

3.3.6菜单配置选项

这个模块提供了以下Linux内核配置选项。

•CONFIG_MMC构建对MMC总线协议的支持。在menuconfig中这个选项在下面可用:

— Device Drivers > MMC/SD/SDIO Card support

—缺省情况下该选项为“Y”。

•CONFIG_MMC_BLOCK构建了对MMC块设备驱动程序的支持可以用来挂载文件系统。在menuconfig中这个选项在下面可用:

— Device Drivers > MMC/SD Card Support > MMC block device driver

—缺省情况下该选项为“Y”。

•CONFIG_MMC_SDHCI_ESDHC_IMX用于i.MX USDHC端口。在menuconfig中这个选项在下面:

— Device Drivers > MMC/SD Card Support > Secure Digital Host Controller Interface support > SDHCI support on the platform-specific bus > SDHCI platform support for the eSDHC i.MX controller

要将SDHCI驱动程序编译为可加载模块应该选择如下所示的几个选项:

CONFIG_MMC_SDHCI=m它可以在Device Drivers > MMC/SD Card Support > Secure Digital Host Controller Interface support中找到

CONFIG_MMC_SDHCI_PLTFM=m它可以在Device Drivers > MMC/SD Card Support > Secure Digital Host Controller Interface support > SDHCI support on the platform-specific bus上找到

CONFIG_MMC_SDHCI_ESDHC_IMX=y它可以在Device Drivers > MMC/SD Card Support > Secure Digital Host Controller Interface support > SDHCI support on the platform-specific bus > SDHCI platform support for the Freescale eSDHC i.MX controller

要将SDHCI驱动程序编译为内置模块应该选择如下所示的几个选项:

CONFIG_MMC_SDHCI=y它可以在Device Drivers > MMC/SD Card Support > Secure Digital Host Controller Interface support 上找到

CONFIG_MMC_SDHCI_PLTFM=y它可以在Device Drivers > MMC/SD Card Support > Secure Digital Host Controller Interface support > SDHCI support on the platform-specific bus上找到。

CONFIG_MMC_SDHCI_ESDHC_IMX=y它可以在Device Drivers > MMC/SD Card Support > Secure Digital Host Controller Interface support > SDHCI support on the platform-specific bus > SDHCI platform support for the Freescale eSDHC i.MX controlle

•CONFIG_MMC_UNSAFE_RESUME用于使用MMC/SD/SDIO卡的嵌入式系统。在menuconfig中这个选项在下面:

3.3.7绑定设备树

所需的属性:

•compatible:应该是"fsl,-esdhc"

reg:应该包含eSDHC寄存器的位置

•interrupt:应该包含eSDHC中断

可选的属性:

•non-removable:表示卡已与主机永久连接

•fsl, wp-internal:表示使用控制器内部写保护

•cd-gpios:指定用于卡检测的GPIOs

•wp-gpios:指定写保护的GPIOs

•fsl, delay-line:为eMMC DDR模式指定延迟线值

Example:usdhc@02194000 { /* uSDHC2 */

compatible = "fsl,imx6q-usdhc";

reg = <0x02194000 0x4000>;

interrupts = <0 23 0x04>;

clocks = <&clks 164>, <&clks 164>, <&clks 164>;

clock-names = "ipg", "ahb", "per";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_usdhc2_1>;

cd-gpios = <&gpio2 2 0>;

wp-gpios = <&gpio2 3 0>;

bus-width = <8>;

no-1-8-v;

keep-power-in-suspend;

enable-sdio-wakeup;

status = "okay";

};

参考:

• Documentation/devicetree/bindings/mmc/fsl-imx-esdhc.txt

• arch/arm/boot/dts/imx6*.dtsi

3.3.8编程接口

该驱动程序实现了MMC总线协议所需的功能以与i.MX uSDHC模块进行接口。请参阅由build生成的Linux文档:make htmldocs。

3.3.9可加载模块操作

SDHCI驱动程序可以构建为可加载或内置模块。

- 如何构建SDHCI驱动程序作为可加载模块。

•CONFIG_MMC_SDHCI=m它可以在Device Drivers > MMC/SD Card Support > Secure Digital Host Controller Interface support 上找到

•CONFIG_MMC_SDHCI_PLTFM=m它可以在Device Drivers > MMC/SD Card Support > Secure Digital Host Controller Interface support > SDHCI support on the platform-specific bus上找到。

•CONFIG_MMC_SDHCI_ESDHC_IMX=y它可以在Device Drivers > MMC/SD Card Support > Secure Digital Host Controller Interface support > SDHCI support on the platform-specific bus > SDHCI platform support for the i.MX eSDHC i.MX controller 上找到

- 如何加载和卸载SDHCI模块。

由于依赖关系按照如下所示的模块顺序加载或卸载模块。

加载模块的命令如下:

• 使用insmod命令加载模块假设是 sdhci.ko 和sdhci-platform.ko 存在于当前目录.

$> insmod sdhci.ko

$> insmod sdhci-platform.ko

•通过modprobe命令加载模块确保 sdhci.ko and sdhci-platform.ko 文件存在于相应的内核模块lib目录

$> modprobe sdhci.ko

$> modprobe sdhci-platform.ko

卸载模块的命令如下.:

• 通过rmsmod 命令卸载.

$> rmsmod sdhci-platform

$> rmsmod sdhci

• 通过modprobe命令卸载模块.

$> modprobe -r sdhci-platform

$> modprobe -r sdhci

3.4 NAND GPMI Flash

3.4.1介绍

MTD (NAND Flash Memory Technology Devices)驱动程序用于通用媒体接口(GPMI)控制器

i.MX 6系列和i.MX 7Dual。

只有实现了特定于硬件的层NAND MTD驱动程序才能运行。其他的功能如Flash读/写/擦除由Linux MTD子系统为NAND设备提供的通用层自动处理。

NAND MTD驱动程序与集成的NAND控制器进行接口该控制器支持文件系统如UBIFS、CRAMFS和JFFS2UBI以及UBIFSCRAMFS和JFFS2。由于NAND Flash技术只支持块访问驱动实现支持对外部NAND Flash芯片的最低级操作如块读、块写、块擦除。因为NAND Flash中的块不能保证是好的NAND MTD驱动程序还能够检测坏块并将该信息传递给上层来处理坏块管理。

3.4.2硬件操作

NAND闪存是一种用于嵌入式系统的非易失性存储设备。

驱动程序不支持随机访问内存的情况下RAM或NOR闪存。对NAND Flash的读写必须通过GPMI完成。NAND Flash是一种适用于大容量存储应用的顺序访问设备。存储在NAND Flash中的代码不能从那里执行。代码必须加载到RAM内存中并从那里执行。i.MX 6包含一个硬件纠错模块。

3.4.3软件操作

Linux中的mtd包括所有内存设备如RAM、ROM和不同种类的NOR/NAND闪存。

MTD子系统提供对所有此类设备的统一访问。在MTD设备之上可以使用Flash文件系统(JFFS2)进行MTD块设备模拟也可以使用UBI层。反过来UBI层可以在卷之上有UBI文件系统也可以在其之上有一个带有常规文件系统(FAT, Ext2/3)的闪存转换层(FTL)。特定于硬件的驱动程序与i.MX 6上的GPMI模块接口。它实现最低级别的操作如读取、写入和擦除。如果启用它还提供有关NAND设备上分区的信息—这些信息必须由平台代码提供。

如果可能NAND驱动程序是可以恢复读/写错误的点。硬件纠错由BCH块执行并由NAND驱动程序代码驱动。

关于NAND驱动程序接口的详细信息可以在www.linux-mtd.infradead.org上找到。

3.4.4基本操作:读写

NAND驱动导出以下回调:

gpmi_ecc_read_page (ECC)

gpmi_ecc_write_page (ECC)

gpmi_read_byte (ECC)

gpmi_read_buf (ECC)

gpmi_write_buf (ECC)

gpmi_ecc_read_oob (ECC)

gpmi_ecc_write_oob (ECC)

从4.1内核开始GPMI驱动程序提供了原始的读/写模式它导出了这些回调:

•gpmi_ecc_read_page_raw(没有ECC)

•gpmi_ecc_write_page_raw(无ECC)

•gpmi_ecc_read_oob_raw(不带ECC)

•gpmi_ecc_write_oob_raw(不带ECC)

这些函数读取所请求的数据量无论是否进行错误纠正。对于read调用gpmi_read_page()函数创建DMA链提交执行然后等待完成。写入情况稍微复杂一些:通过调用gpmi_send_page()来映射和输出要写入的数据。

3.4.5向后兼容性

用户应该知道内核4.1中几个主要的GPMI NAND驱动更改这些更改可能会导致内核升级不兼容。

•通过debugfs将必要的信息导出到用户空间应用程序(kobs-ng)

•新的BCH布局算法

•新的原始读写模式

在内核4.1中NAND GPMI驱动程序通过debugfs将必要的信息导出到上层。最常见的情况是NAND烧录工具kobs-ng。如果不启用debugfs, kobs-ng可能无法完全使用新特性或者可能使用不合适参数。如果自定义内核中没有启用debugfs那么用户需要为kobs-ng提供正确的BCH几何信息和原始访问模式。

在之前的内核中BCH布局可能无法满足NAND芯片最小ECC要求。自Kernel 4.1开始BCH布局算法默认使用NAND所需的ECC强度和步长如果可访问则从ONFI参数中获取。该更改可能与前一个内核中的BCH布局设置不兼容。为了向后兼容,内核和U-boot提供了使用传统BCH布局的开关。

•对于Kernel在设备树文件中添加“fsl,legacy-bch-geometry”。

•对于U-Boot:在单板配置文件中增加“CONFIG_NAND_MXS_BCH_LEGACY_GEO”。

为了对齐必须在内核和U-boot中同时打开/关闭BCH传统布局设置。

Kobs-ng在debugfs中检查内核版本或原始模式标志以确定是否使用新的原始模式来访问NAND芯片。新的kobs-ng完全向后兼容以前的内核而旧版本的kobs-ng不能在内核4.1上工作。

3.4.6纠错

当读取或写入数据到Flash一些位可以翻转。这是正常的行为NAND驱动程序利用各种错误纠正方案来纠正它。可以通过软件或硬件纠错来解决。GPMI驱动程序仅在硬件加速器bch的帮助下使用硬件校正方案。

对于BCH来说2K页的页面布局为(2K + 64) 4K页的页面布局为(4K + 218) 8K页的页面布局为(8K + 448)。

3.4.7启动控制块管理

在启动过程中NAND驱动扫描第一个块以确定是否存在NAND控制块(NCB)。它的存在是通过魔法签名检测的。当发现一个签名时使用汉明码检查引导块候选项是否有错误。如果发现了错误则在可能的情况下修复它们。如果找到NCB则对其进行解析以检索NAND芯片的计时。

所有引导控制块都是在使用用户空间应用程序kobs-ng格式化媒体时创建的。

3.4.8坏块处理

当驱动程序开始时默认情况下它会构建坏块表。可以动态地确定某个块是否坏但为了提高性能这是在启动时进行的。擦除块的缺点是通过检查块的每一页的空闲区域开始的模式来确定的。但如果芯片采用硬件纠错则坏标记会落入ECC字节区域。因此如果使用硬件纠错应移动坏块标记。

3.4.9源代码结构

NAND驱动位于drivers/mtd/ NAND /gpmi-nand中。

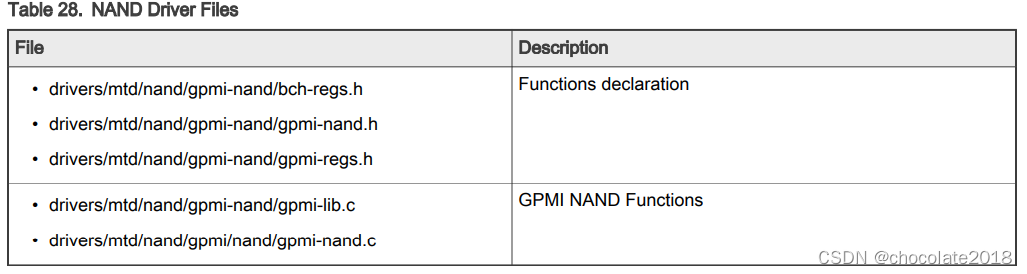

下表列出了NAND驱动程序的源文件。

3.4.10菜单配置选项

要启用NAND驱动程序必须设置以下选项:

•Device Drivers > Memory Technology Device (MTD) support > GPMI NAND Flash Controller driver

此外这些MTD选项必须启用:

•CONFIG_MTD_NAND = [y | m]

•CONFIG_MTD = y

•CONFIG_MTD_BLOCK = y

此外必须启用以下UBI选项:

•CONFIG_MTD_UBI = y

•CONFIG_UBIFS_FS = y

3.5四串行外设接口(QuadSPI)

3.5.1介绍

Quad串行外围接口(QuadSPI)块作为一个接口到一个或两个外部串行闪存设备每个设备最多有四条双向数据线。

支持以下特性:

•灵活的序列引擎支持各种flash厂商设备。

•单、双、四、八进制操作模式。

•DDR/DTR模式数据产生在串行闪存时钟的每个边缘。

•支持在DDR和SDR模式下进行数据采样的闪存数据选通信号。

•DMA支持通过AMBA AHB总线(64位宽度接口)或IP寄存器空间(32位访问)读取RX缓冲区数据。

3.5.2硬件操作

在一些单板上配备了Quad SPI NOR - N25Q256A而在其他一些单板上配备了S25FL128S。请检查单板上的Quad SPI NOR类型然后进行正确配置。

N25Q256A是一种高性能的多输入/输出串行闪存器件。创新、高性能、双和四输入/输出指令使读取和程序操作的传输带宽增加了一倍或四倍。内存被组织为512 (64kb)个主扇区可以一次擦除64kb的扇区。设备支持3字节或4字节地址模式访问超过128mb的内存。当启用4字节地址模式时所有需要地址的命令都必须使用4字节地址模式命令输入和退出: 输入4字节地址模式命令和退出4字节地址模式命令。4字节地址模式也可以通过非易失性配置寄存器启用。内存可以使用三种不同的协议操作: 扩展SPI标准SPI协议升级为双和四操作、双输入/输出SPI和四输入/输出SPI。每个协议都有唯一的命令来执行DTR模式下的READ操作。这使得高数据吞吐量同时运行在较低的时钟频率。

S25FL128S是flash非易失性存储产品。它通过串行外围接口(SPI)连接到主机系统。

支持传统的SPI单位串行输入输出(single I/O或SIO)以及可选的2位(Dual I/O或DIO)和4位(Quad I/O或QIO)串行命令。它还增加了对SIO、DIO和QIO的双数据速率(DDR)读取命令的支持这些命令在时钟的两端传输地址和读取数据。

3.5.3软件操作

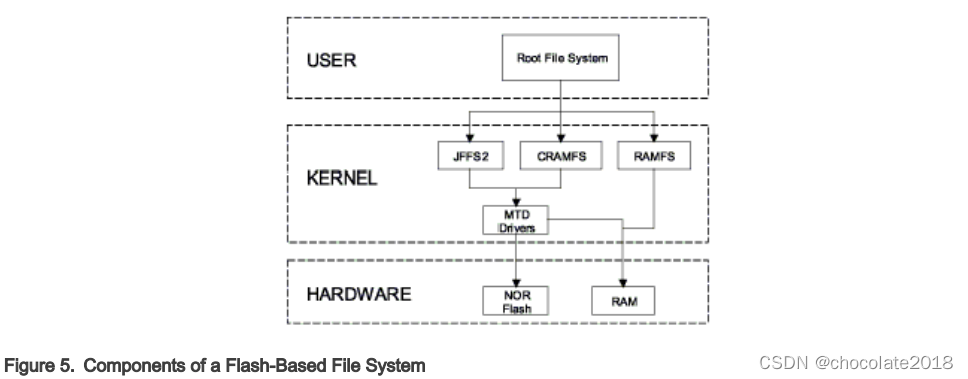

在一个基于flash的嵌入式Linux系统中许多Linux技术一起工作来实现一个文件系统。下图说明了一些标准组件之间的关系。

Linux操作系统的MTD子系统是到内存设备(如Flash和RAM)的通用接口提供对物理内存设备的简单读、写和擦除访问。称为mtdblock的设备可以由JFFS、JFFS2和CRAMFS文件系统挂载。Quad SPI NOR MTD驱动是基于内核中的MTD数据闪存驱动增加了SPI访问。在初始化阶段Quad SPI NOR MTD驱动程序通过读取JEDEC ID来检测数据Flash。驱动添加MTD设备。SPI NOR MTD驱动程序还提供了读取、写入和擦除NOR Flash的接口。

3.5.4驱动特性

这个Quad NOR驱动实现支持以下特性:

•上层MTD驱动所需信息。

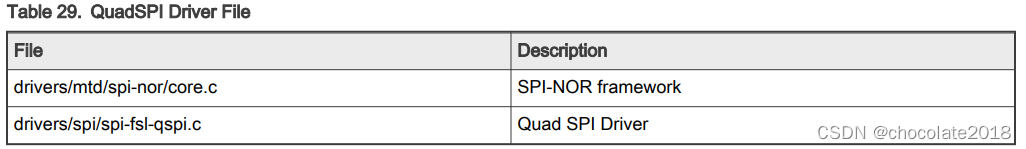

3.5.5源代码结构

3.5.6菜单配置选项

要启用Quad SPI驱动程序必须设置以下选项:

Device Drivers >Memory Technology Device (MTD) support > Freescale Quad SPI controller

对于配置将这些设置为启用Quad Spi。

•CONFIG_MTD_SPI_NOR: SPI NOR的框架可以被SPI设备驱动程序和SPI-NOR设备驱动程序使用。

•CONFIG_SPI_FSL_QUADSPI:在主模式下启用对quadspi控制器的支持。

3.6 SATA

3.6.1介绍

SATA AHCI驱动程序基于Linux内核的块设备基础设施的LIBATA层。关于SATA的详细硬件操作在Synopsys DesignWare Cores SATA AHCI文档中有详细介绍该文档名为SATA_Data_Book.pdf。

3.6.2单板配置选项

关闭电源安装SATA电缆和硬盘驱动器。

3.6.3软件操作

关于libata api的详细信息请参见libata开发人员指南。

SATA AHCI驱动程序基于Linux内核的块设备基础设施的LIBATA层。i.MX集成AHCI linux驱动程序结合标准AHCI驱动程序处理集成i.MX SATA AHCI控制器的细节而LIBATA层理解和执行SATA协议。SATA设备(比如硬盘)通过/dev/sda*接口向用户空间中的应用程序公开。文件系统构建在块设备上。AHCI指定了集成的DMA引擎它在DMA传输模式中帮助SATA控制器硬件。

3.6.4源代码结构

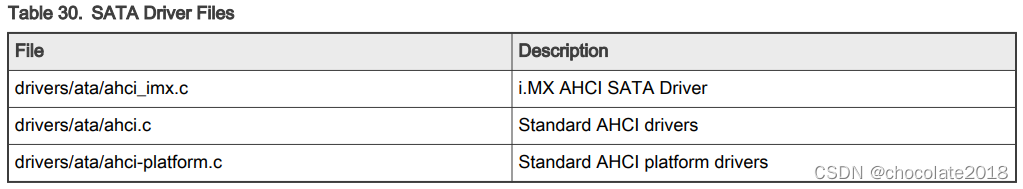

标准的AHCI和AHCI平台驱动程序是用来做实际的SATA操作。

3.6.5菜单配置选项

SATA驱动提供的Linux内核配置如下:

Symbol: AHCI_IMX [=y]

Type : tristate

Prompt: Freescale i.MX AHCI SATA support

Location:

-> Device Drivers

-> Serial ATA and Parallel ATA drivers (ATA [=y])

-> Platform AHCI SATA support (SATA_AHCI_PLATFORM [=y])

在busybox中在“Linux System Utilities”下启用“fdisk”。

3.6.6编程接口

SATA驱动程序的应用程序接口是/dev/sda*上的标准POSIX设备接口(例如:打开、关闭、读、写和ioctl)。

3.6.7用法示例

请注意:

当初始化少量SATA磁盘时可能会有一个已知的错误消息例如:

ata1.00:序列号不匹配’090311PB0300QKG3TB1A’ != "

Ata1.00:重新验证失败(errno= 19)

这一点应该被忽略。

- 在构建内核和SATA AHCI驱动程序并进行部署之后启动目标并以root用户登录。

- 确保AHCI和AHCI平台驱动程序构建在内核中或加载到内核中。

你应该会看到类似如下的消息:

ahci: SSS flag set, parallel bus scan disabled

ahci ahci: AHCI 0001.0300 32 slots 1 ports 3 Gbps 0x1 impl platform mode

ahci ahci: flags: ncq sntf stag pm led clo only pmp pio slum part ccc apst

scsi0 : ahci_platform

ata1: SATA max UDMA/133 mmio [mem 0x02200000-0x02203fff] port 0x100 irq 71

ata1: SATA link up 3.0 Gbps (SStatus 123 SControl 300)

ata1.00: ATA-8: SAMSUNG HM100UI, 2AM10001, max UDMA/133

ata1.00: 1953525168 sectors, multi 0: LBA48 NCQ (depth 31/32)

ata1.00: configured for UDMA/133

scsi 0:0:0:0: Direct-Access ATA SAMSUNG HM100UI 2AM1 PQ: 0 ANSI: 5

sd 0:0:0:0: [sda] 1953525168 512-byte logical blocks: (1.00 TB/931 GiB)

sd 0:0:0:0: [sda] 4096-byte physical blocks

sd 0:0:0:0: [sda] Write Protect is off

sd 0:0:0:0: [sda] Write cache: enabled, read cache: enabled, doesn't support DPO or FUA

sda: sda1

sd 0:0:0:0: [sda] Attached SCSI disk

您可以使用标准的Linux实用程序在应用程序挂载和使用的驱动器(例如:fdisk和mke2fs)上进行分区并创建文件系统。

驱动器及其分区的设备节点出现在/dev/sda*下面。例如要检查驱动器的基本内核设置请执行hdparm /dev/sda。

3.6.8用法示例

创建分区

可以使用下面的命令查询硬盘的容量。如果硬盘是预格式化的这个命令会显示硬盘的大小、分区和文件系统类型:

$fdisk -l /dev/sda

如果硬盘未格式化请使用以下命令在硬盘上创建分区:

$fdisk /dev/sda

在分区之后创建的文件类似于/dev/sda[1-4]。

块读写测试:dd命令用于读写块。注意这个命令会破坏硬盘上的分区和文件系统。

要清除卡的前5 KB请执行以下操作:

$dd if=/dev/zero of=/dev/sda1 bs=1024 count=5

答复应如下:

5+0 records in

5+0 records out

要将文件内容写入卡请输入以下文本用要写入的文件名替换文件名执行以下操作:

$dd if=file_name of=/dev/sda1

要从卡读取1KB的数据输入以下文本将要写入的文件的名称替换为output_file执行如下操作:

$dd if=/dev/sda1 of=output_file bs=1024 count=1

文件系统测试

使用mkfs.vfat or mkfs.ext2格式化硬盘分区取决于文件系统:

$mkfs.ext2 /dev/sda1

$mkfs.vfat /dev/sda1

挂载文件系统的方式如下:

$mkdir /mnt/sda1

$mount -t ext2 /dev/sda1 /mnt/sda1

挂载完成后可以在“/mnt/sda1”目录下进行操作。

卸载文件系统的步骤如下:

$umount /mnt/sda1