FPGA结构分析——IDDR,网口储备点1

| 阿里云国内75折 回扣 微信号:monov8 |

| 阿里云国际,腾讯云国际,低至75折。AWS 93折 免费开户实名账号 代冲值 优惠多多 微信号:monov8 飞机:@monov6 |

先抛出几个问题

1.什么是 IDDR IDDR的作用是什么使用场景

2. IDDR结构是什么样都有哪些端口端口属性都是什么

3. IDDR原语结构参数属性说明

4. IDDR时序是什么样

1.什么是 IDDR IDDR的作用是什么使用场景

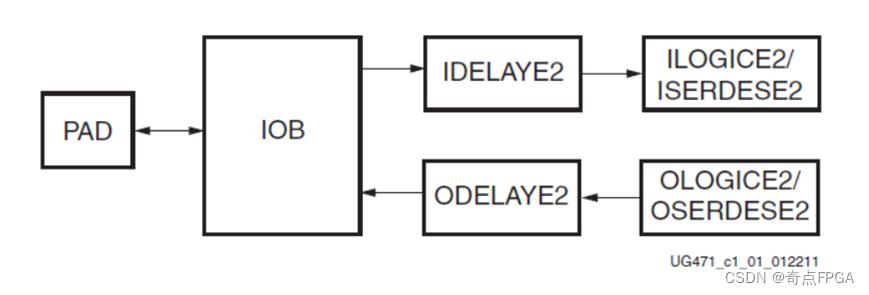

IDDR全称 input double date rate可以将双沿时钟的上升沿、下降沿数据信号转换为单沿数据信号通常使用在串转并数据设计中如网口的RGMII信号转换为GMII信号

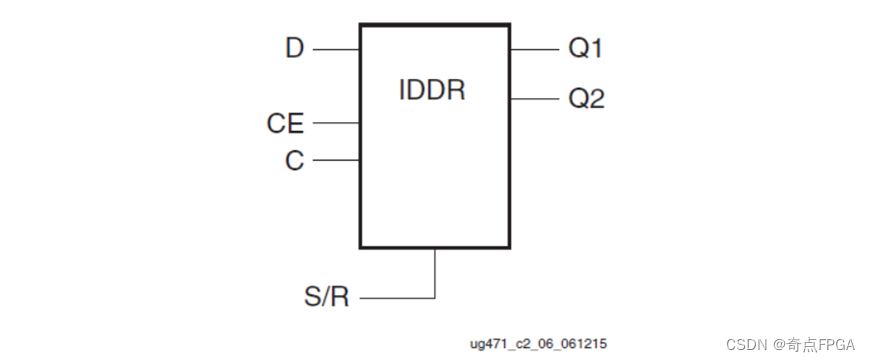

2. IDDR结构是什么样都有哪些端口端口属性都是什么

端口说明

C同步时钟输入端口

CE时钟使能端口高电平有效

D双沿数据输入端口

S/R置位复位管脚

Q1C端口上升沿数据

Q2C端口下降沿数据

3.IDDR原语结构参数属性说明

原语结构

IDDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_inst (

.Q1(Q1), // 1-bit output for positive edge of clock

.Q2(Q2), // 1-bit output for negative edge of clock

.C(C), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D(D), // 1-bit DDR data input

.R(R), // 1-bit reset

.S(S) // 1-bit set

);

参数属性说明

DDR_CLK_EDGE设置IDDR相对于时钟端口的边沿工作模式共三种模式在第4小节会具体说明

INIT_Q1/ INIT_Q2设置Q1、Q2端口初始值

SRTYPE设置置/复位异步或者同步默认异步

4.IDDR时序是什么样

IDDR有三种采集模式在原语中由DDR_CLK_EDGE参数进行设置分别为“OPPOSITE_EDGE”、“SAME_EDGE”和“SAME_EDGE_PIPELINED”模式。

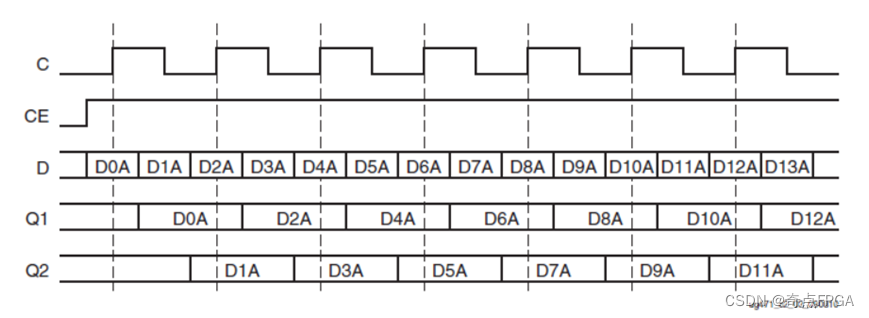

OPPOSITE_EDGE模式的时序图如下图所示Q1端在时钟的上升沿更新Q2端在时钟的下降沿更新更准确地来说在时钟的上升沿Q1端数据稳定在在时钟的下降沿Q2端数据稳定。

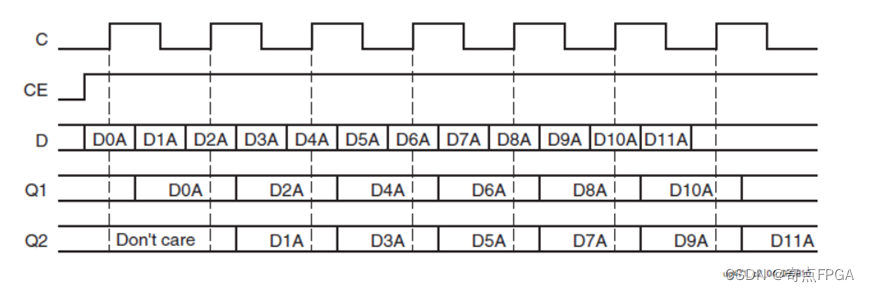

SAME_EDGE模式的时序图如下图所示Q1端、Q2端都在时钟的上升沿更新但D0和D1出现相差一个时钟。

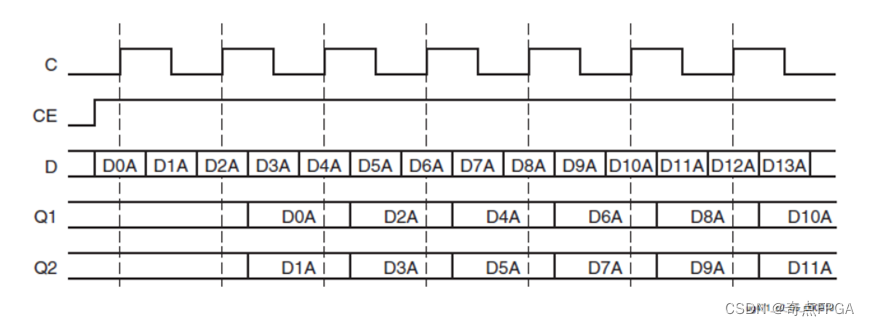

SAME_EDGE_PIPELINED模式的时序图如下图所示Q1端、Q2端都在时钟的上升沿更新但D0和D1出现在同一个时钟。

一般情况使用第三种SAME_EDGE_PIPELINED模式不需要考虑多余的时钟延迟就能直接使用串转并后的数据。

5.几点思考

1.在FPGA中经常出现的问题就是时钟和数据的对齐这个问题的原因有很多比如器件差异、PCB走线等等那么在使用IDDR时如何校正这一块就是一个难题通常可以采用修改时钟相位偏移来解决比如使用FPGA 内侧的时钟资源进行相位偏移或者IOLOGIC侧IODELAY原语进行延迟等本质上都是为了使得时钟与数据的对齐

2.有IDDR就会有ODDR比如网口中通过ODDR将GMII转化为RGMII在下一篇继续阐述

| 阿里云国内75折 回扣 微信号:monov8 |

| 阿里云国际,腾讯云国际,低至75折。AWS 93折 免费开户实名账号 代冲值 优惠多多 微信号:monov8 飞机:@monov6 |